As a printed circuit board (PCB) operates, power dissipation in active components raises their junction temperature, transferring heat into conductors and the substrate. Since most PCB materials have low thermal conductivity, this can lead to thermal issues such as hot spots and elevated temperatures. To ensure components remain within their safe operating limits, effective heat dissipation techniques are essential for directing heat away from critical areas.

Thermal management strategies can be categorized as passive or active, both aiming to remove heat from components and disperse it—either into the surrounding air or to cooler regions of the board.

- Passive cooling relies on natural heat transfer mechanisms, such as conduction, convection, and radiation, without requiring additional energy input.

- Active cooling employs more aggressive methods, such as fans, liquid cooling, or thermoelectric coolers, to forcibly dissipate heat.

In many high-power or densely packed PCB designs, a combination of passive and active techniques provides optimal thermal performance. By integrating both approaches, designers can achieve efficient heat dissipation while maintaining reliability.

The Heat Challenge in PCB Design

Heat generation is an inevitable byproduct of electrical current flowing through components on a PCB. While some heat is normal, excessive thermal buildup can lead to numerous problems, including:

- Reduced component lifespan

- Decreased overall system reliability

- Potential circuit malfunctions

- Thermal stress and physical damage to the PCB

Understanding the impact of heat on PCBs is the first step in developing effective strategies for thermal management.

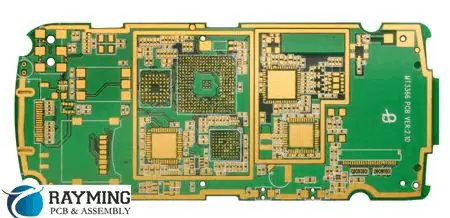

Innovative Heat Dissipation Strategies for PCBs

To combat the challenges posed by heat in PCB design, engineers and designers have developed a variety of innovative techniques. Let’s explore some of the most effective methods for optimizing heat dissipation in PCBs.

1. Implementing Active Cooling Solutions

One of the most direct approaches to managing heat in PCBs is through the use of active cooling solutions. These methods involve the addition of components specifically designed to remove heat from the system.

Integrating Cooling Fans

Cooling fans are a popular choice for active heat dissipation in PCB designs. They work by creating airflow across the board, which helps to carry away heat generated by components. When implementing cooling fans:

- Consider the placement carefully to maximize airflow across hot spots

- Choose fans with appropriate CFM (cubic feet per minute) ratings for your specific heat load

- Ensure proper mounting to minimize vibration and noise

Incorporating Heat Sinks

Heat sinks are passive components that increase the surface area available for heat dissipation. They are typically made of materials with high thermal conductivity, such as aluminum or copper. To effectively use heat sinks:

- Select heat sinks with appropriate fin designs for your space constraints

- Use high-quality thermal interface materials to ensure good contact with hot components

- Consider combining heat sinks with fans for enhanced cooling performance

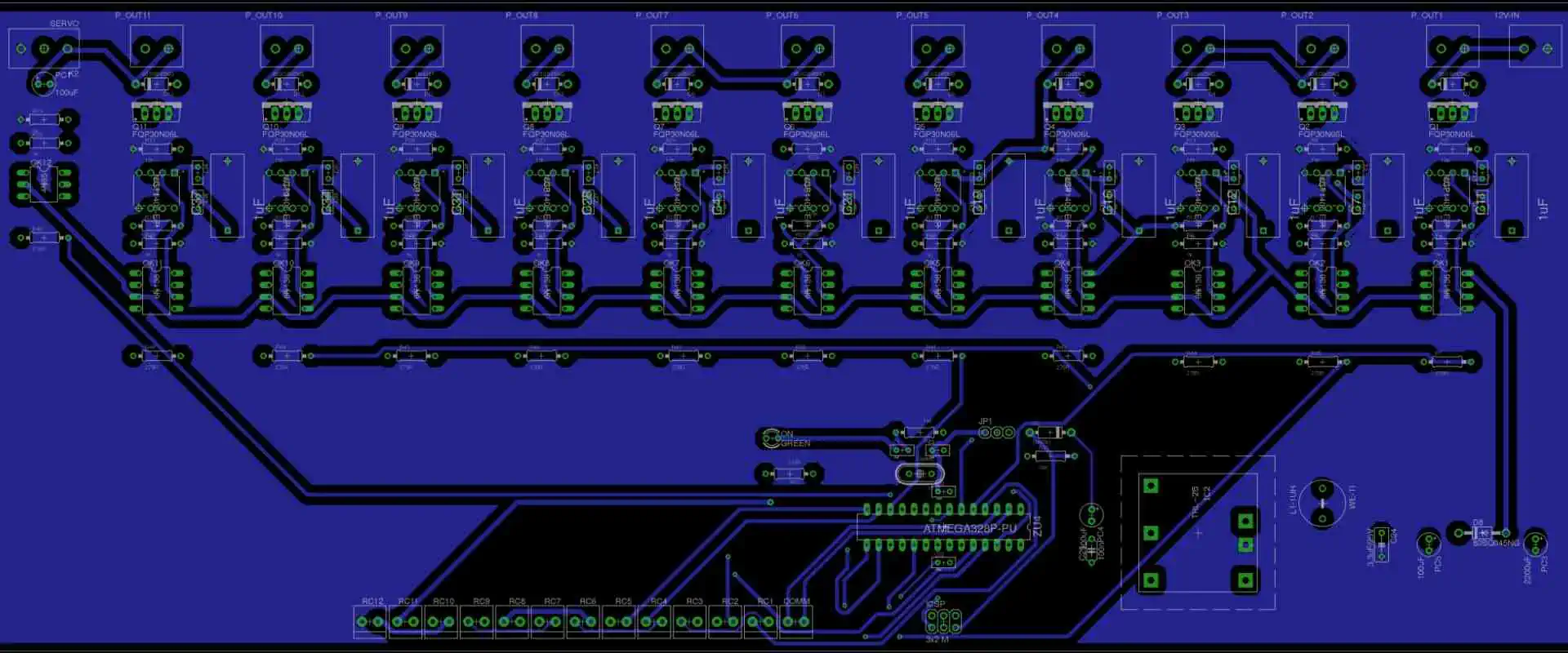

2. Optimizing PCB Copper Usage

Copper plays a crucial role in heat dissipation within PCBs due to its excellent thermal conductivity. By strategically utilizing copper in your PCB design, you can significantly improve heat management.

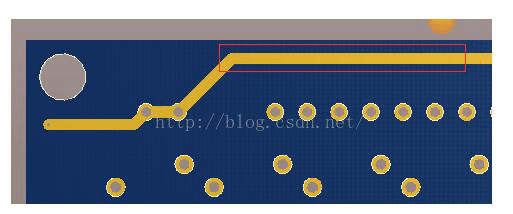

Leveraging Thick Copper Traces

Increasing the thickness of copper traces can enhance their ability to conduct heat away from components. Consider the following when implementing thick copper traces:

- Use wider traces for power and ground connections

- Increase copper weight in areas with high heat generation

- Balance trace thickness with manufacturing constraints and cost considerations

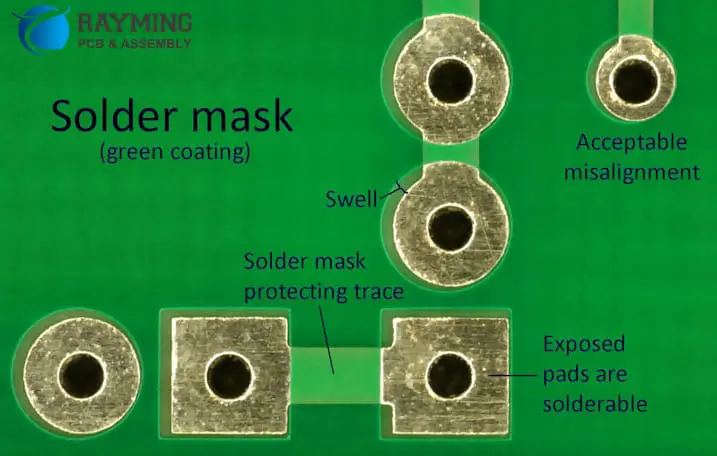

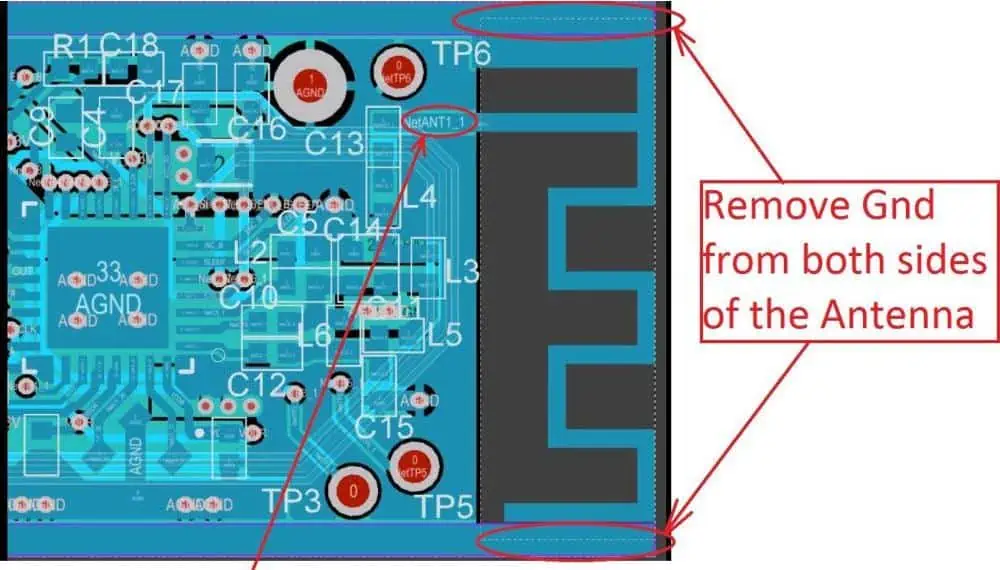

Implementing Copper Planes

Copper planes provide large areas for heat dissipation and can help distribute heat more evenly across the board. To effectively use copper planes:

- Dedicate entire layers to power and ground planes when possible

- Use thermal relief connections to prevent excessive heat sinking during soldering

- Consider split planes to isolate noisy digital circuits from sensitive analog sections

Read more about:

3. Exploring Advanced Cooling Technologies

As PCB designs become more complex, advanced cooling technologies are being developed to meet the growing demands of heat dissipation.

Utilizing Heat Pipes

Heat pipes are sealed tubes containing a working fluid that efficiently transfers heat from one location to another. They can be particularly useful in designs where space is limited. When considering heat pipes:

- Evaluate the orientation and length requirements for optimal performance

- Choose appropriate working fluids based on your operating temperature range

- Combine heat pipes with heat sinks or spreaders for enhanced cooling

Implementing Liquid Cooling Systems

For high-power applications, liquid cooling systems can offer superior heat dissipation compared to air-based methods. While more complex to implement, they can provide significant thermal management benefits:

- Consider closed-loop systems for easier maintenance and reduced risk of leaks

- Select appropriate coolants based on thermal properties and compatibility with materials

- Design the system to minimize the risk of electrical shorts in case of leaks

Material Selection for Enhanced Thermal Management

The choice of materials used in PCB construction plays a critical role in heat dissipation. By selecting the right materials, you can significantly improve the thermal performance of your PCB design.

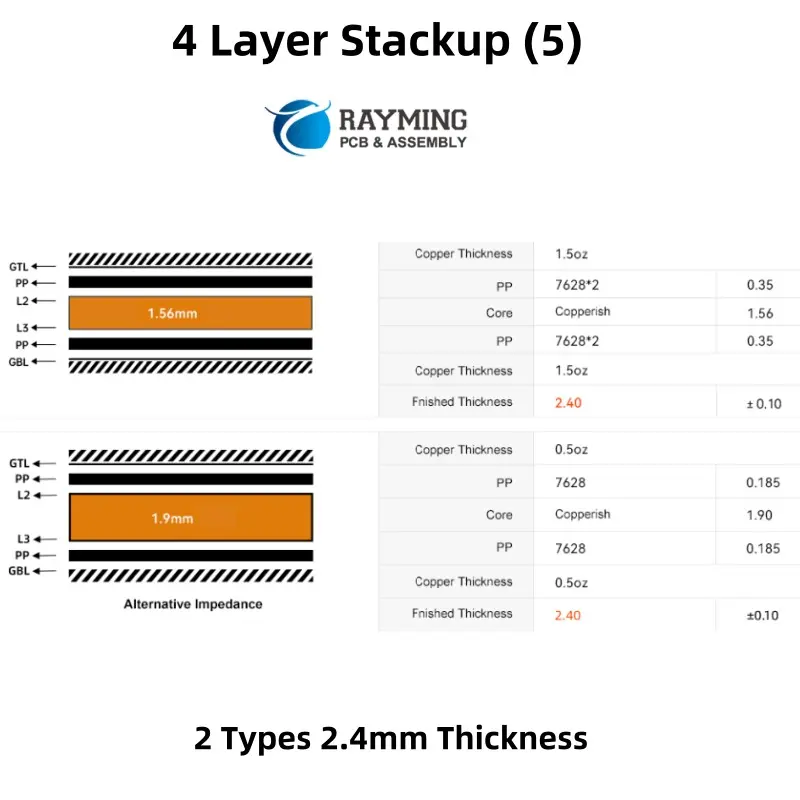

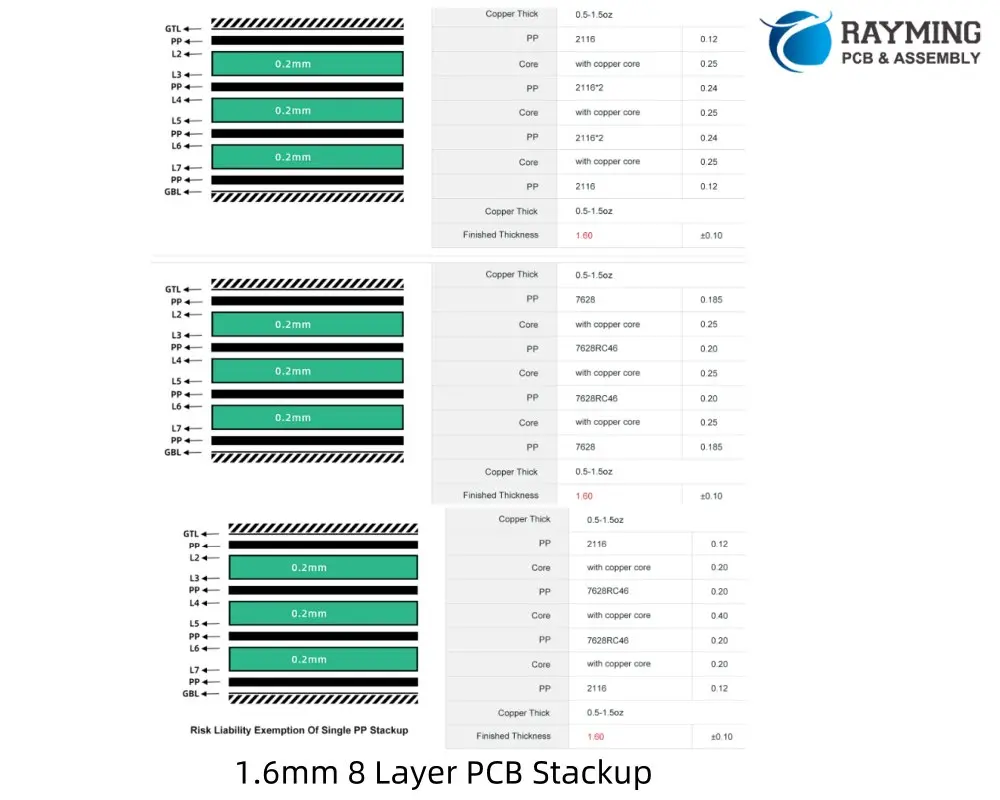

Substrate Materials: Balancing Performance and Cost

The substrate material forms the foundation of the PCB and greatly influences its thermal characteristics. Common options include:

- FR-4: Standard and cost-effective, but with limited thermal conductivity

- Aluminum PCBs: Excellent thermal conductivity, ideal for LED applications

- Ceramic substrates: High thermal conductivity, suitable for high-frequency applications

- Polyimide: Good for flexible PCBs with moderate thermal requirements

When selecting substrate materials, consider:

- The thermal conductivity required for your application

- Cost constraints and production volume

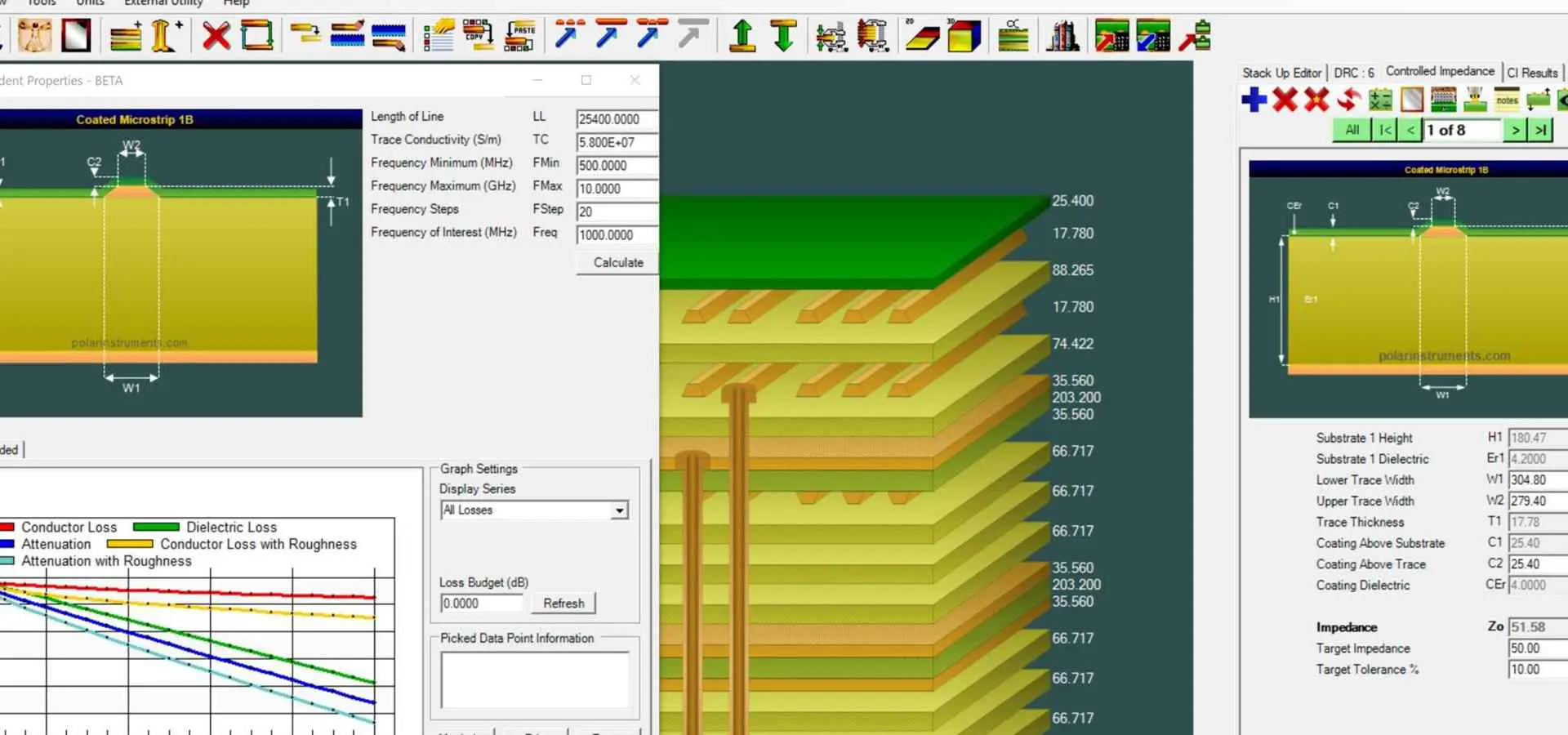

- Electrical properties such as dielectric constant and loss tangent

- Mechanical properties like flexibility and dimensional stability

Thermal Interface Materials: Bridging the Gap

Thermal interface materials (TIMs) are crucial for ensuring efficient heat transfer between components and heat sinks or other cooling solutions. Popular TIMs include:

- Thermal greases

- Phase change materials

- Thermal pads

- Thermally conductive adhesives

When choosing TIMs, consider factors such as:

- Thermal conductivity

- Ease of application and rework

- Long-term stability and reliability

- Compatibility with your assembly process

Thermal Management Techniques for Compact PCB Designs

As electronic devices continue to shrink in size, managing heat dissipation in compact PCB designs becomes increasingly challenging. Here are some strategies to improve thermal performance in space-constrained designs:

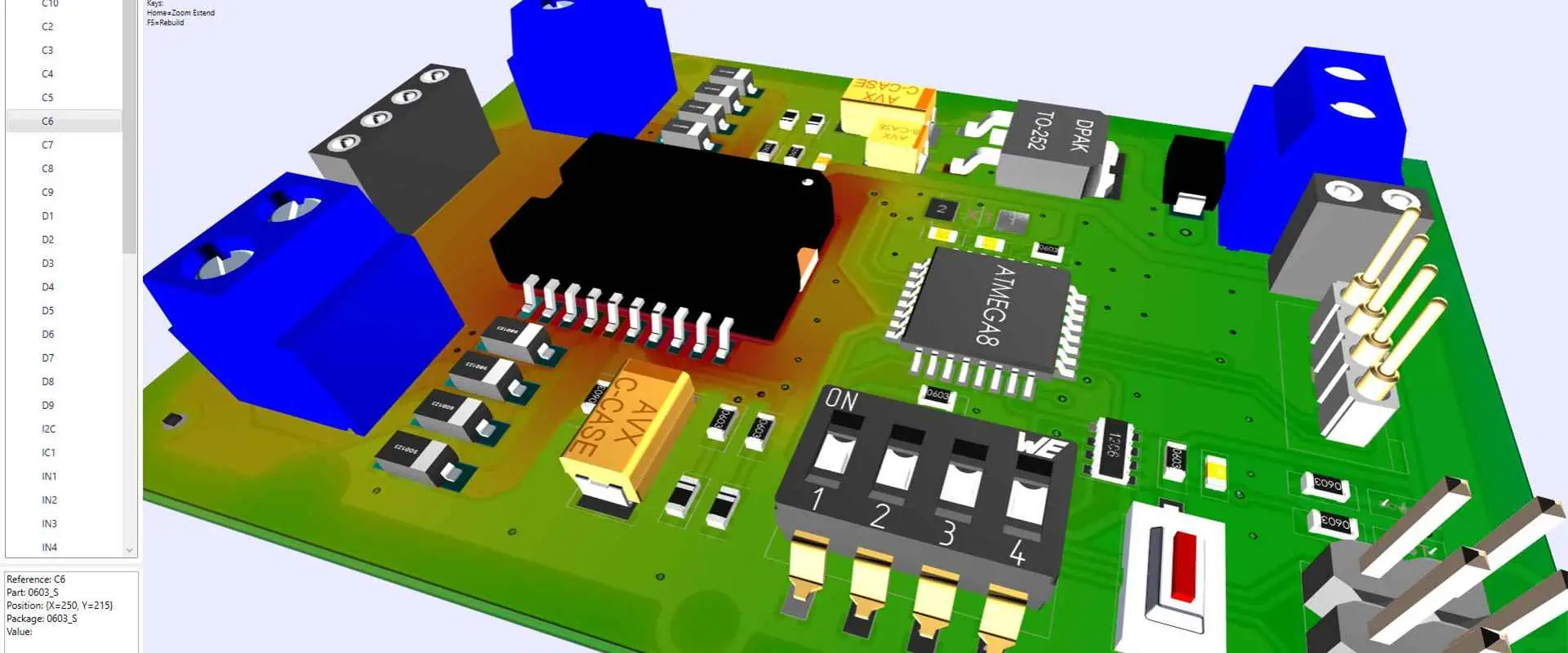

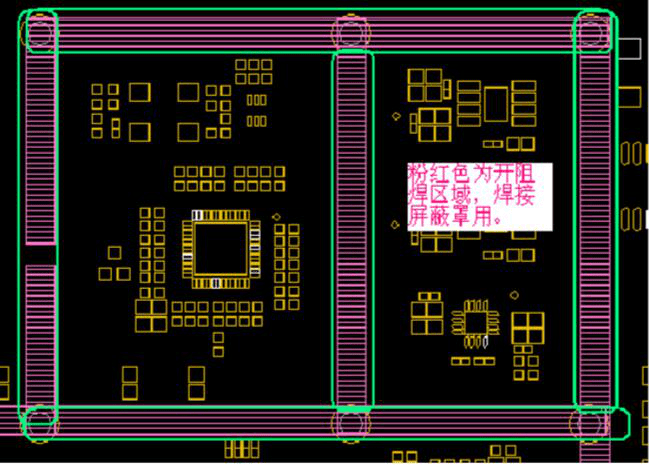

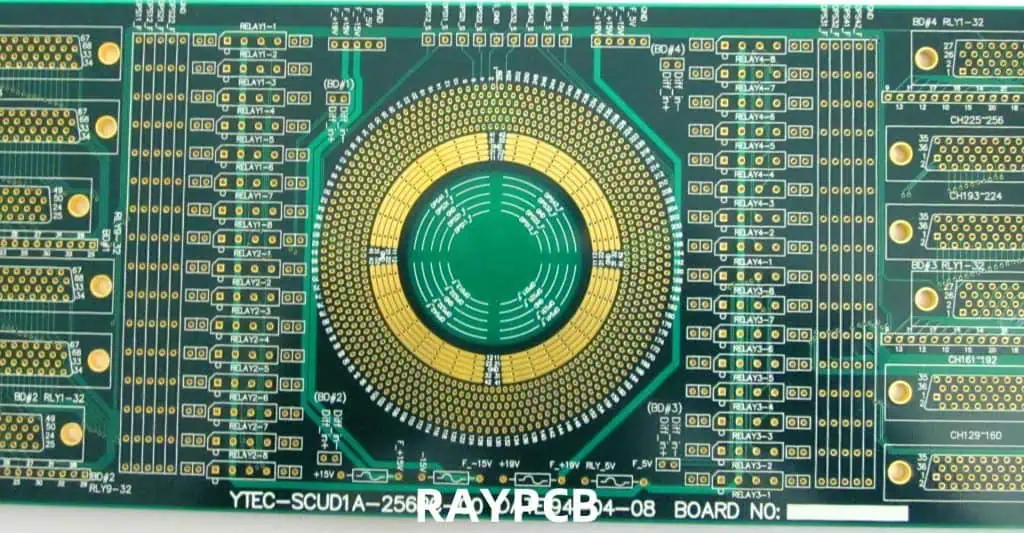

Optimizing Component Placement

Careful component placement can significantly impact heat distribution across the board:

- Group high-heat components together and place them near the board’s edges

- Use thermal simulations to identify and address potential hot spots

- Consider the impact of component placement on airflow patterns

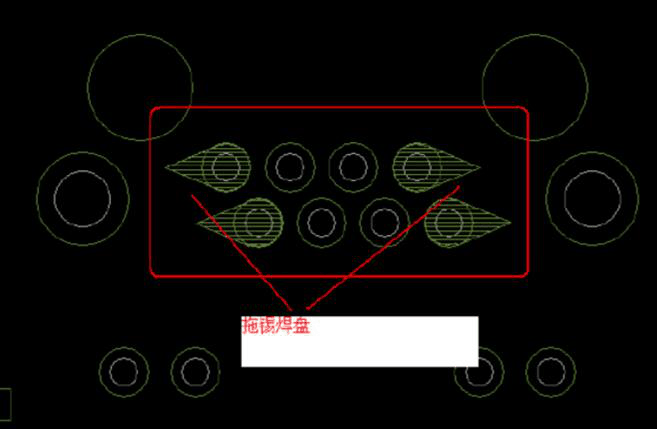

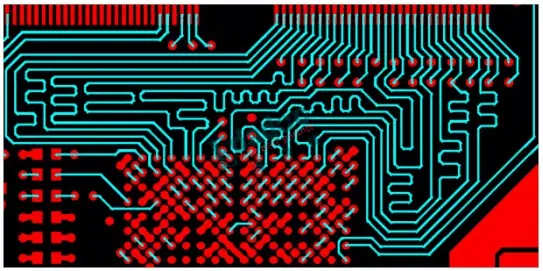

Leveraging Thermal Via Arrays

Thermal vias are plated through-holes that help conduct heat between PCB layers. To effectively use thermal via arrays:

- Place them directly under or around hot components

- Use a grid pattern to maximize heat transfer

- Fill vias with thermally conductive materials for enhanced performance

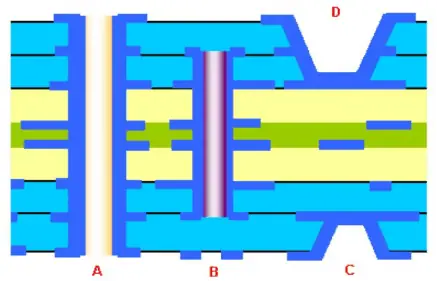

Implementing Copper Coin Technology

Copper coins are thick pieces of copper inserted into the PCB to provide localized heat spreading. This technique can be particularly effective for managing heat from high-power components in compact designs:

- Use copper coins under components with high thermal output

- Ensure proper integration with the PCB manufacturing process

- Consider combining copper coins with other cooling techniques for optimal results

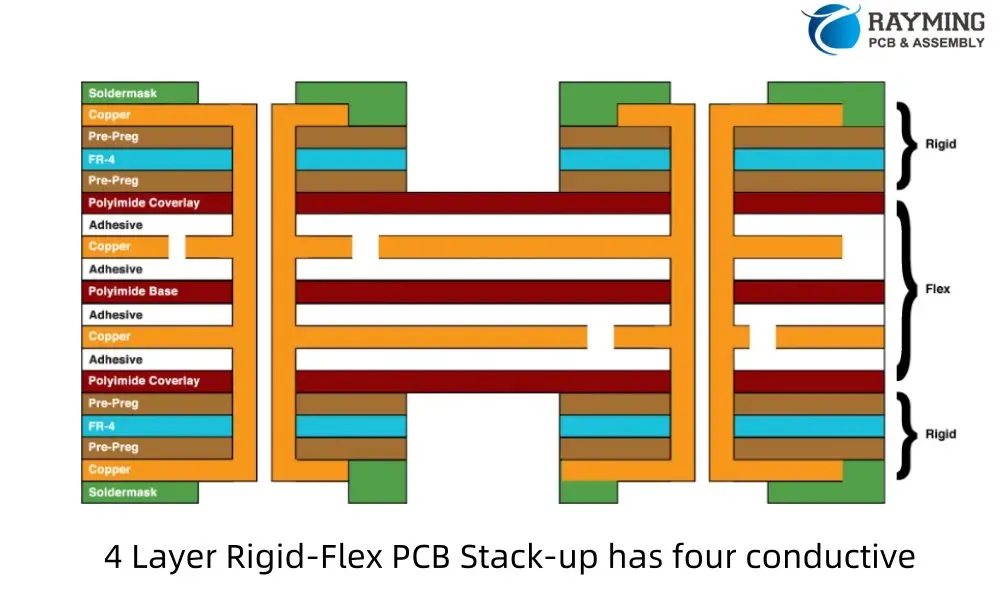

Heat Dissipation in Flexible PCB Designs

Flexible PCBs present unique challenges for heat dissipation due to their thin and bendable nature. However, several strategies can be employed to manage thermal issues in flex circuits:

Material Selection for Flex PCBs

Choose materials that balance flexibility with thermal performance:

- Polyimide-based substrates offer good thermal stability

- Consider hybrid designs with rigid sections for improved heat dissipation

- Use thermally conductive adhesives for bonding layers

Implementing Copper Patterns

Strategic use of copper can enhance heat dissipation in flex circuits:

- Utilize copper planes where possible, especially in areas with high heat generation

- Consider hatched ground planes to maintain flexibility while improving thermal performance

- Use thicker copper weights in critical areas, balancing thermal needs with flexibility requirements

Incorporating Thermal Management Layers

For applications with higher thermal demands, consider adding dedicated thermal management layers:

- Integrate heat-spreading materials like graphite or aluminum

- Use thermally conductive but electrically insulating materials to maintain signal integrity

- Design thermal layers to work in conjunction with the circuit’s bending requirements

Conclusion: A Holistic Approach to PCB Heat Dissipation

Effective heat dissipation in PCB design requires a comprehensive approach that considers various factors, including:

- Component selection and placement

- Material choices for substrates and thermal interfaces

- Implementation of active and passive cooling solutions

- Optimization of copper usage and layout design

- Utilization of advanced thermal management techniques

By carefully considering these aspects and implementing appropriate strategies, designers can create PCBs that effectively manage heat, ensuring optimal performance and longevity of electronic devices. As technology continues to advance, staying informed about the latest developments in thermal management techniques and materials will be crucial for creating efficient and reliable PCB designs.

Remember, the key to successful heat dissipation in PCB design lies in finding the right balance between thermal performance, cost-effectiveness, and manufacturing feasibility. By adopting a holistic approach and leveraging the techniques discussed in this article, you can optimize your PCB designs for superior heat dissipation and overall performance.