Introduction

EMI or electromagnetic interference shielding refers to techniques used for suppressing electromagnetic interference generated by electronic devices. EMI shielding blocks electromagnetic waves from reaching or escaping the device using conductive materials that reflect or absorb radiated energy.

This article provides a comprehensive overview of EMI shielding including:

- Basics of electromagnetic interference

- Need for shielding electronics

- Shielding principles and materials

- Shielding methods and design

- Shielding measurement

- Applications and trends

Understanding EMI shielding concepts enables designing robust electronic products that function reliably by containing interference.

Basics of Electromagnetic Interference

Electromagnetic interference (EMI) refers to disturbances caused due to unwanted generation, propagation and reception of electromagnetic energy that can potentially degrade the performance of electronics.

Sources of EMI

- Switching signals and clocks

- Power supply rectification

- Data and control buses

- High speed serial links

- Displays and touch interfaces

- DC-DC converters

- Motors and relays

Effects of EMI

- Increased error rates in data transmission

- Noise on audio and video signals

- False switching and spurious behaviors

- Degradation of signal integrity

- Equipment malfunctions and shutdowns

With greater computing speeds, closed system architectures and sensitive analog interfacing, EMI mitigation through shielding becomes vital for reliability.

Need for Shielding Electronics from EMI

Shielding is essential for ensuring proper functioning of electronic equipment due to:

Susceptibility Requirements

- Electronics need protection from external interference sources

Emission Requirements

- Prevent device emissions from disrupting other equipment

Regulatory Compliance

- Meet EMC/EMI standards for electronic products

Signal Integrity

- Guard noise sensitive analog signals and sensor interfaces

Safety

- Avoiding equipment malfunctions and shutdowns

Security

- Contain compromising emanations from circuits

From laptops to medical devices, automotive electronics to LTE basestations, shielding helps electronics operate reliably and safely by suppressing interference.

Shielding Methods and Materials

EMI shielding aims to contain EMI through reflection, absorption or diffusing the emitted energy using conductive materials surrounding the source. Common shielding methods include:

Faraday Cage Shielding

An enclosure made of conducting material that blocks external fields. Works by induced surface currents cancelling incident fields.

Conductive Coatings

Paints loaded with conductive fillers like nickel, copper or carbon particles that reflect/absorb EMI when coated on plastics.

Conductive Plastics

Plastics mixed with fillers like stainless steel fibers, carbon particles or nickel coated graphite that provide shielding through absorption when molded into enclosures.

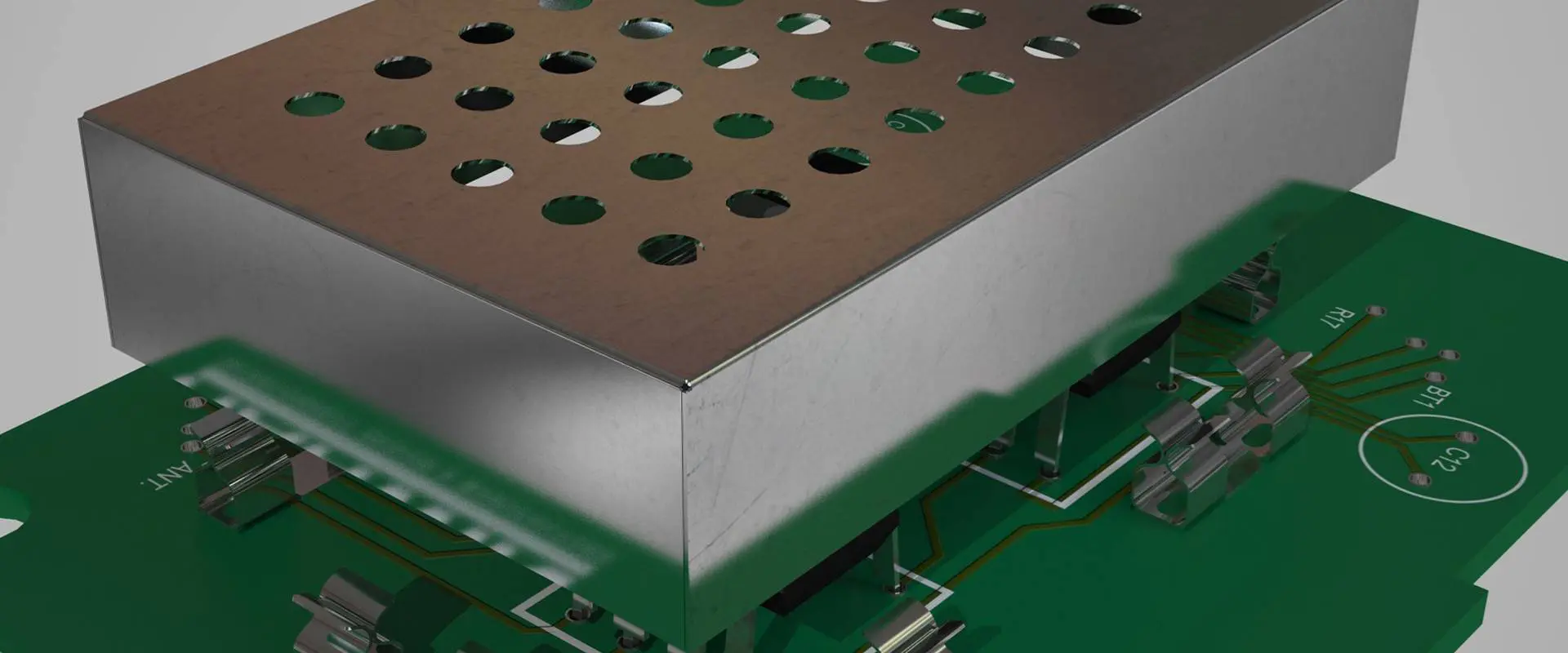

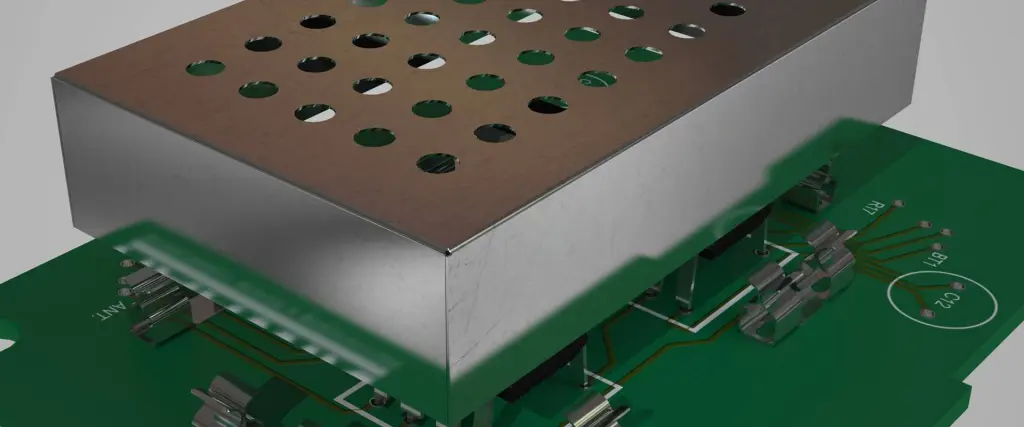

Board Level Shielding

Small metal cans soldered onto PCBs enclosing components needing isolation. Effective for blocking high frequency noise.

Cable Shielding

Foils or braided mesh surrounding cables that isolates signals from external noise pickup/radiation.

Component Shielding

Shielding integrated into component construction. Examples include metal core PCBs, shielded connectors, absorptive cables.

EMI Gaskets

Conductive elastomer gaskets placed between metallic chassis/covers that compress during closure to block EMI leakage through gaps.

Optimal shielding combines multiple techniques tailored to the frequency range, emissions sources, mechanical design and cost.

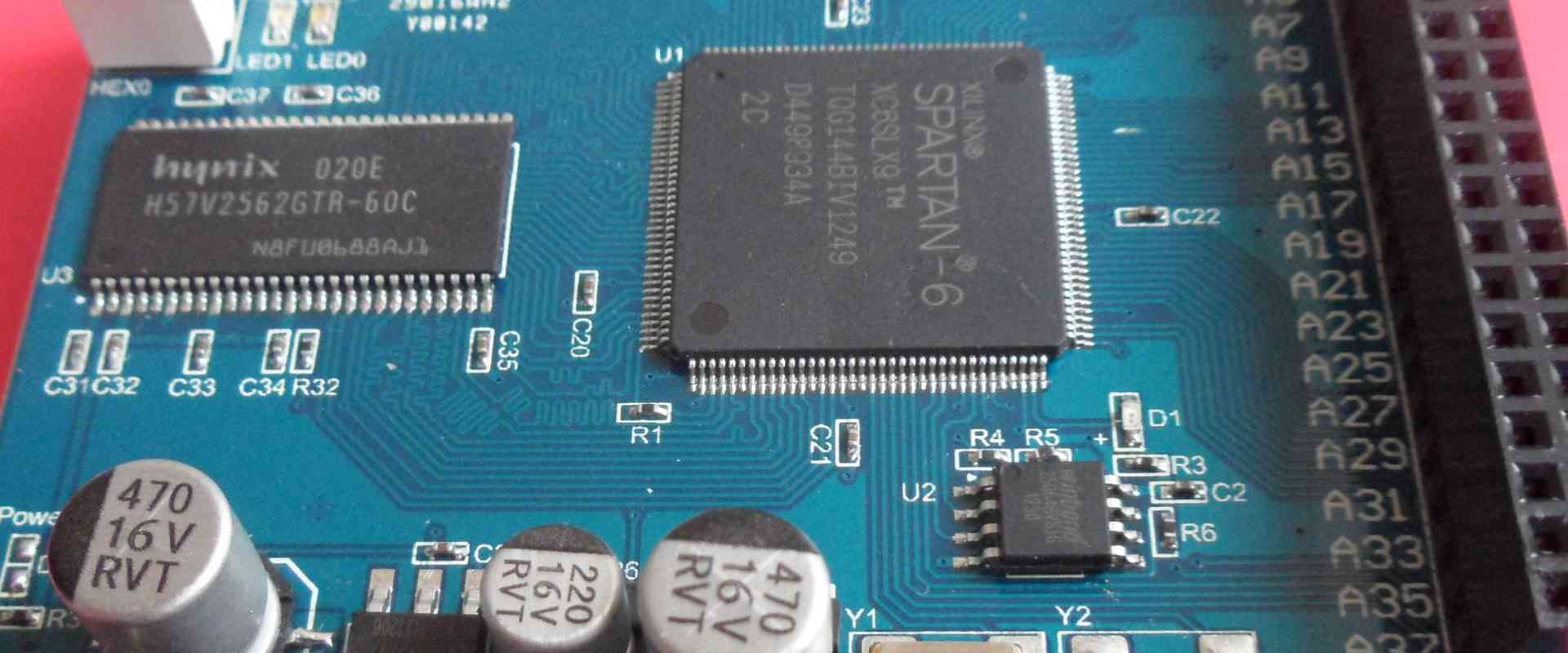

Shielding Materials

Materials commonly used for EMI shielding include:

- Metals – Steel, nickel, copper, aluminium, tin

- Conductive paints – Nickel/copper filled latex, epoxy, acrylic

- Conductive coatings – Vacuum deposited aluminium on plastic

- Conductive plastics – ABS, polycarbonate with Ni-coated graphite filler

- Conductive foams – Silver coated open cell PU foam

- EMI absorbers – Ferrite tiles, carbon loaded foam absorbers

- EMI gaskets – Conductive elastomers with silver plating

Selecting suitable materials involves balancing shielding effectiveness, manufacturability, corrosion resistance, cost constraints and mechanical needs.

Shielding Design Considerations

Some key aspects for effective EMI shielding implementation are:

Governing Standards

- Understand applicable emissions and immunity standards like FCC, CISPR 11

Frequency Range

- Blocking lower frequencies requires thicker, solid metal shields unlike high frequencies

Shield Location

- Close proximity to sources provides optimal containment

Seams and Gaps

- Minimize openings for leakage of unwanted emissions

Grounding

- Robust grounding of enclosure using multiple low impedance paths

Filtered Connectors

- Prevent noise coupling through shields via connectors

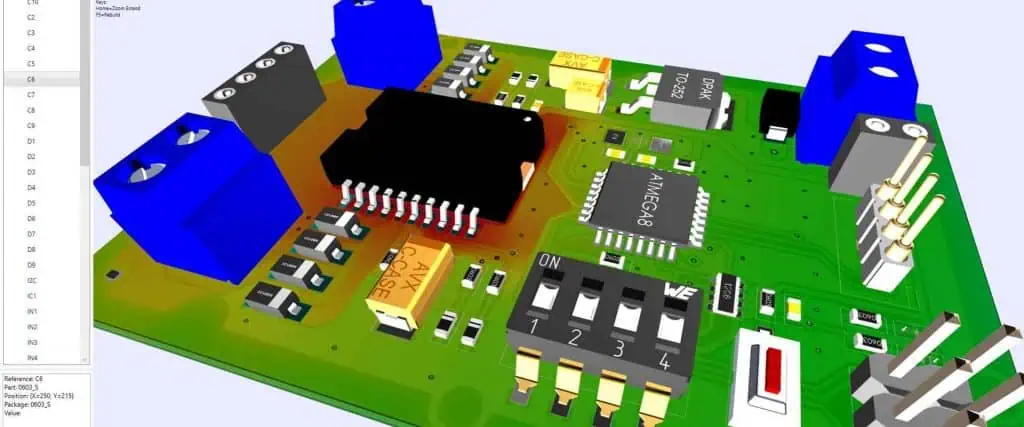

PCB Layout

- Careful component placement, routing and stackups to isolate noise sources and victims

Simulation

- Model shields and analyze with full-wave solvers to predict resonances

An optimized shielding system requires a holistic approach across mechanical, electrical and electronic design.

Shielding Performance Metrics

Shielding effectiveness indicates the reduction in radiated and conducted interference by shields and is expressed in dB. Key metrics are:

Plane Wave Shielding Effectiveness (PWSE)

Measures far-field attenuation when plane EM waves impact the shield. Important for emissions containment.

Near Field Shielding Effectiveness (NFSE)

Measures shielding performance for near-field electric and magnetic coupling. Crucial for immunity and signal isolation.

Transfer Impedance (ZT)

Determines conductivity across the shield between source and victim. Lower ZT indicates better absorption.

Insertion Loss

Measures the reduction in conducted interference from source to victim through shield. Similar concept as transfer impedance.

These parameters help evaluate material suitability and design robustness during shielding development. Shielding performance varies with frequency and needs to be validated across the spectrum.

EMI Shielding Measurement

Measuring the shielding effectiveness quantitatively helps assess design choices and improvements. Common measurement methods are:

Anechoic Chamber Testing

Full compliance testing method with antennas transmitting and receiving through the shielding barrier characterizing both plane wave and near field shielding. Provides wide frequency characterization in controlled lab environment.

GTEM Cell Testing

Uses a tapered septum transmission line to evaluate shielding effectiveness. Can test electric, magnetic and plane wave attenuation. Portable for spot measurements.

Shielded Box Method

Simple setup with noise generator and receiver placed inside and outside a shielded test enclosure to evaluate insertion loss at various points across frequency.

MESA Imaging

Scanning imaging system that maps emissions sources and propagation to pinpoint leakage points needing mitigation.

Validated measurements are crucial during prototyping to tailor the design before final compliance testing.

EMI Shielding Applications

EMI shielding is widely used in electronic products including:

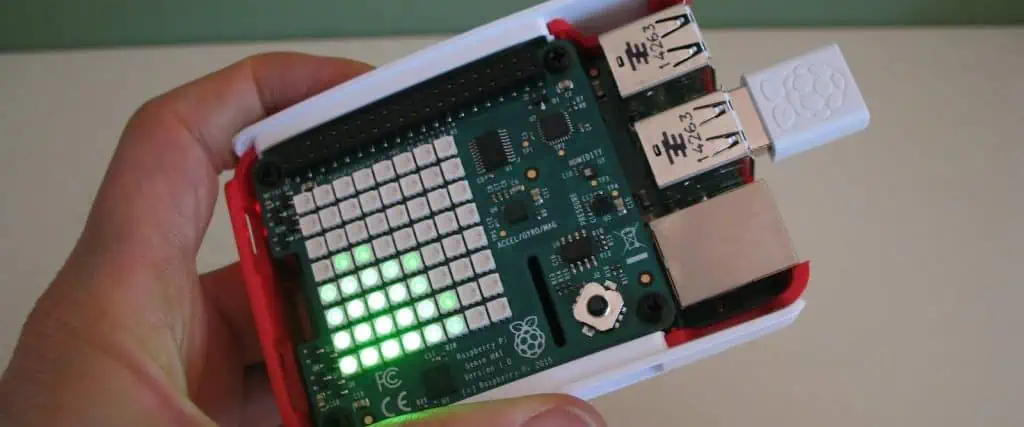

Laptops, smartphones, wearables, home appliances, game consoles

Automotive

Engine control units, infotainment systems, LIDAR modules

Aerospace

Avionics, flight control systems, communications

Medical

Monitoring equipment, implants, scanning systems

Instrumentation

Test and measurement equipment

Industrial

Automation controllers, motor drives, robotics

Communications

5G small cells, private networks, base stations

Any application where electronics need to operate reliably in noisy environments relies on EMI shielding principles implemented through careful mechanical, electrical and PCB design.

EMI Shielding Technology Trends

Advances in materials and manufacturing are expanding shielding capabilities:

- 3D printing – Additively built metal enclosures with complex geometries

- EMI paints – High aspect ratio carbon nanotubes for conductive coatings

- Hybrid coatings – Composite paints combining copper and nickel for increased conductivity

- Thin-profile shields – Flexible conductive tapes for tight space applications

- Structural electronics – Shielding integrated into load bearing structures

- MIT materials – Metamaterials, fractal geometries for improved absorption

- Graphene composites – Graphene infused plastics for light yet effective shielding

- AI-driven design – Optimizing shielding performance using simulations and generative design

- Expanded applications – Effective shielding demands from electric vehicles, IoT endpoints and medical devices

With electronics getting more compact, efficient and operating at higher frequencies, shielding implementation is becoming more critical across application sectors.

Conclusion

As an indispensable technique for ensuring proper functioning and emission compliance of electronic equipment, EMI shielding encompasses specialized materials, design practices and measurements. Shielding methods from conductive coatings to faraday cages along with advanced materials like graphene and metamaterials provide a robust toolkit to contain radiated interference. With electronics advancement leading to increased interference susceptibility and emissions, shielding development using physics-driven modeling and AI-based design techniques promises to be a crucial competitive advantage for developing reliable, secured and compliant products.

What is EMI Shielding? – FQA

Q1. What is the purpose of EMI shielding in electronic products?

EMI shielding blocks electromagnetic interference from entering or escaping the device using conductive materials. This ensures proper functioning and meets EMC/EMI standards.

Q2. What are some common EMI shielding methods?

Shielding approaches include faraday cages, conductive coatings/plastics, board-level shields, cable shields, component shields, absorbers and EMI gaskets between metallic enclosures.

Q3. How is shielding performance quantified?

Key parameters are plane wave shielding effectiveness, near field shielding, transfer impedance and insertion loss. These determine attenuation across frequency spectrum.

Q4. What materials are commonly used for EMI shielding?

Materials used are metals like steel, nickel, copper, conductive paints, plastics, coatings, foams, absorbers, gaskets containing metallic fillers.

Q5. What are some considerations in EMI shielding design?

Considerations include applicable EMI standards, noise frequencies, shield location, seams/gaps minimization, grounding, filtered connectors, enclosure material and PCB layout techniques.