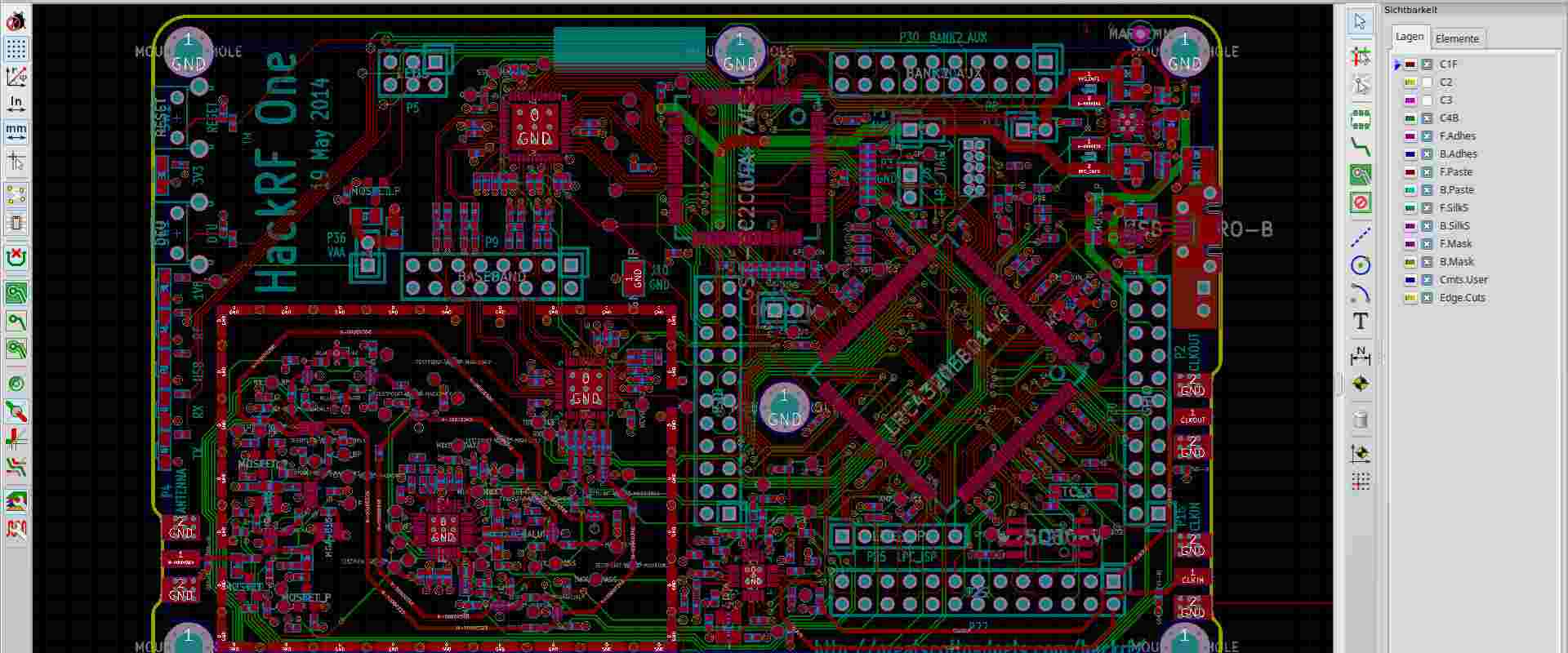

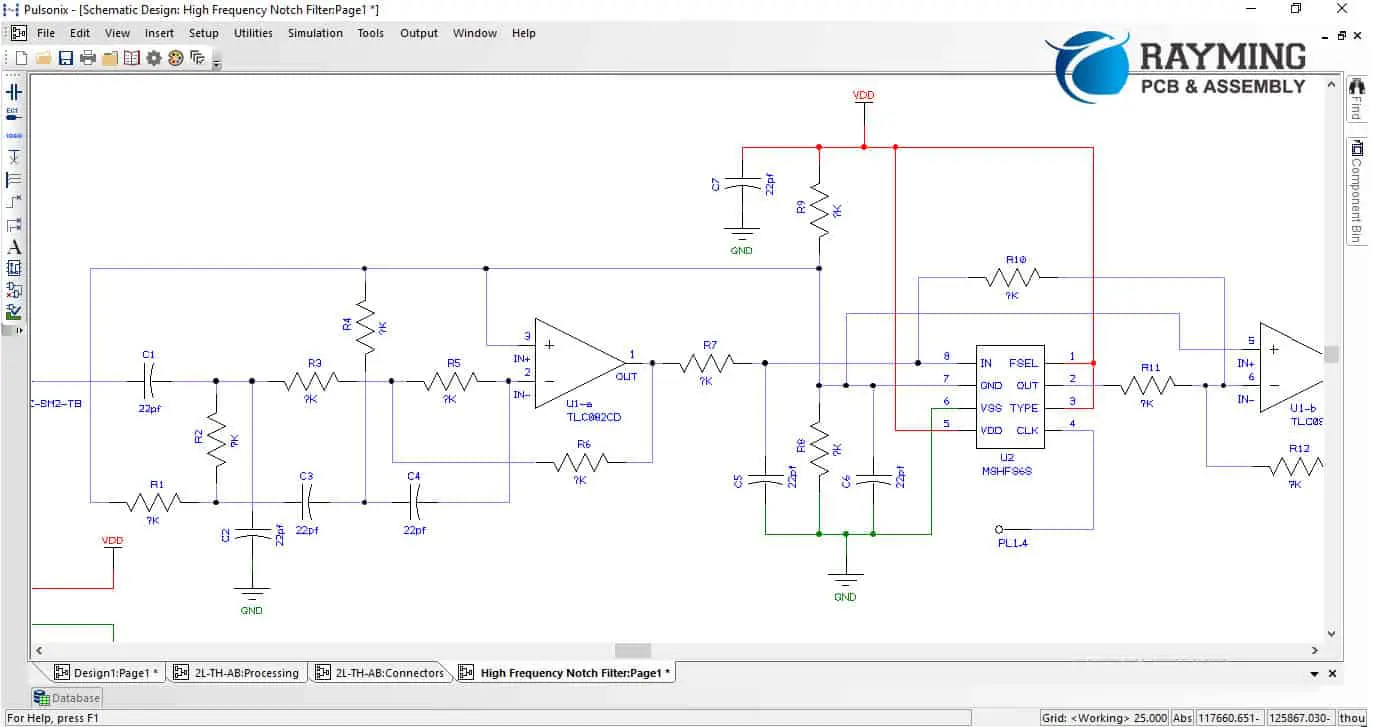

KiKAD is a very effective tool for the design of Printed Circuit Boards (PCBs). The tool has numerous characteristics along with capability of designing PCB layout such as ability of generating Bill of Materials, Schematics design, and auto conversion of schematics to PCB layout etc. However, this article is comprised of all relevant information required for the acquisition of Bill of Material (BOM) having information of all relevant Component Placement List (CPL). The Component Placement List is also sometimes referred to as Pick and Place or Centroid file when use of the tool KiCAD is considered. The following is detailed method for the generation of Bill of Materials along with Component Placement List.

The Generation of Bill of Material Files

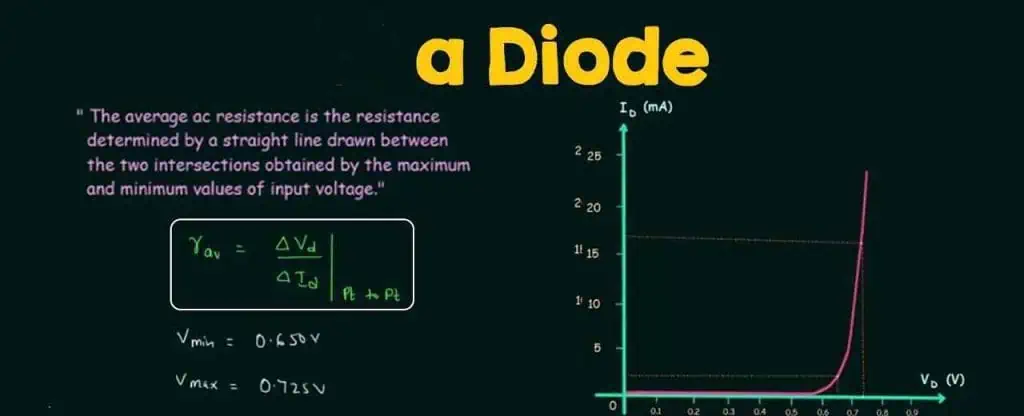

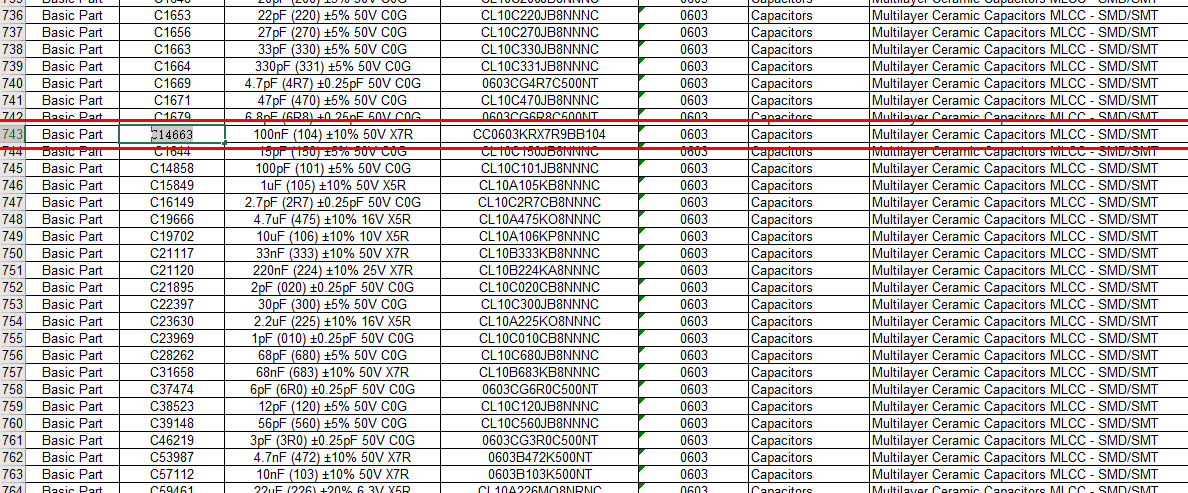

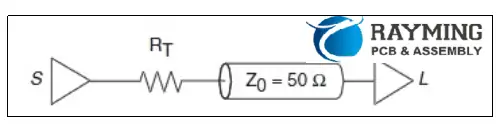

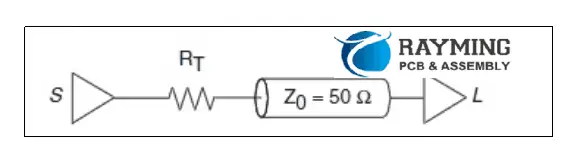

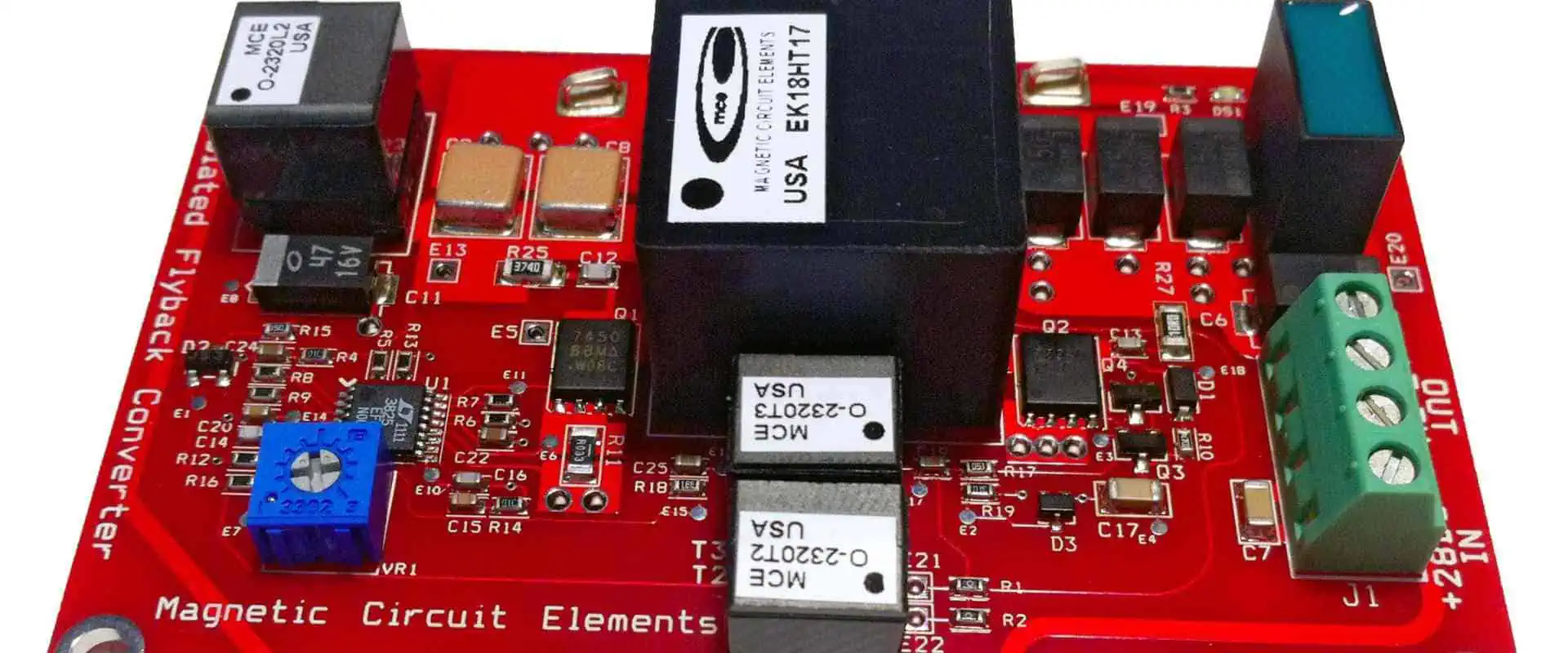

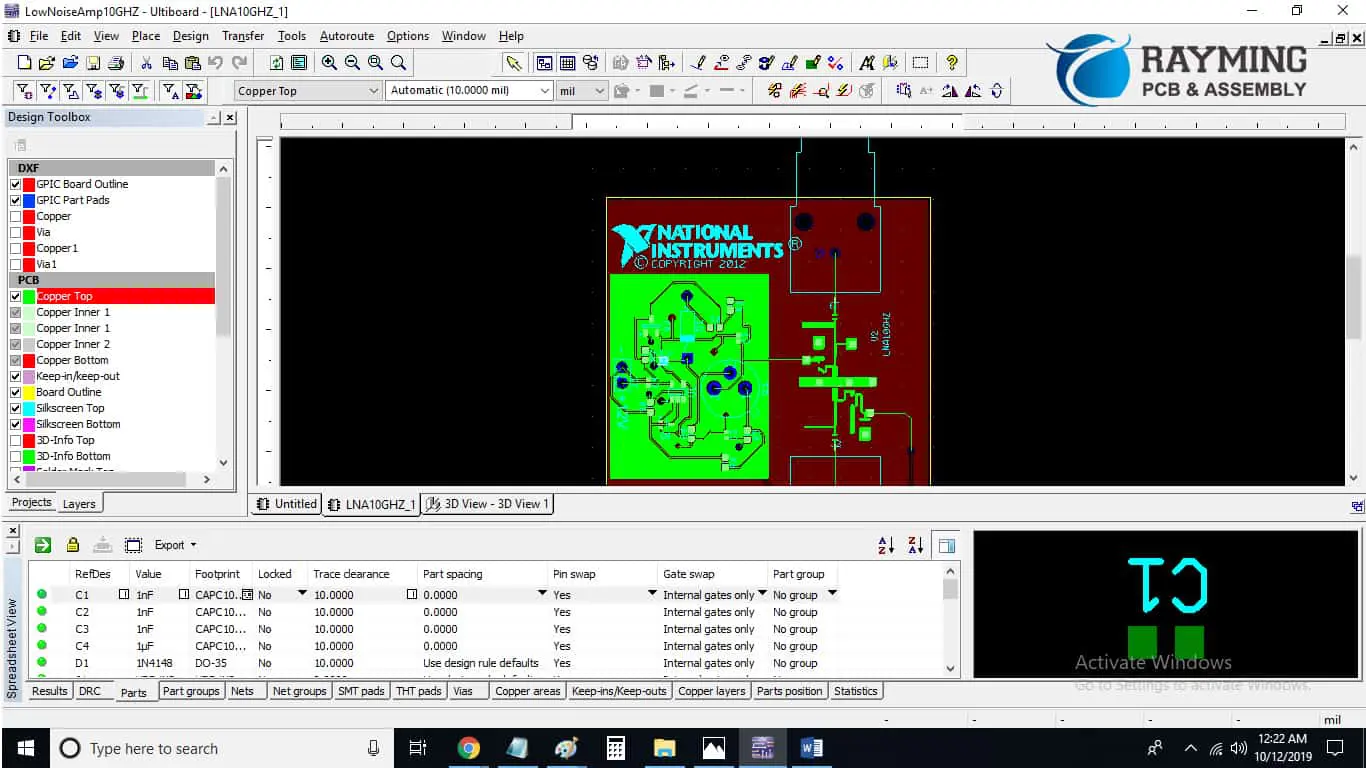

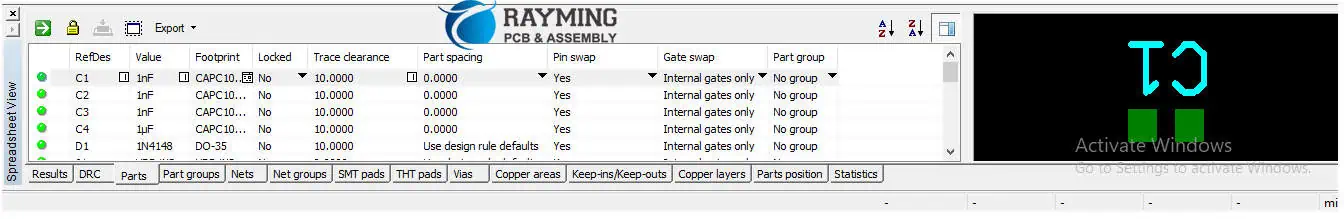

The Bill of Materials is having required information about the entire electronic components which are used in the layout of PCBs. The BOM is also having information of the exact locations where each of the component has been placed. Considering an example of certain PCB having various components at different positions such as T1, R1, and C1 etc. being printed on the layout of PCB, however the manufacturer is not aware of the component being used on these positions. Therefore, BOM list will enable the manufacturer to have an idea of the component being used on these locations being transistor, capacitor, resistor, or inductor etc. The BOM is very important when it comes to the assembly process. However, bear in mind that BOM is a simple excel or text file which has information of all components and its exact location. In case if you don’t like the auto generated format of KiCAD, you can also make the BOM in excel spread sheets yourself with your convenience. The image below is illustrating a simple BOM list extracted from KiCAD.

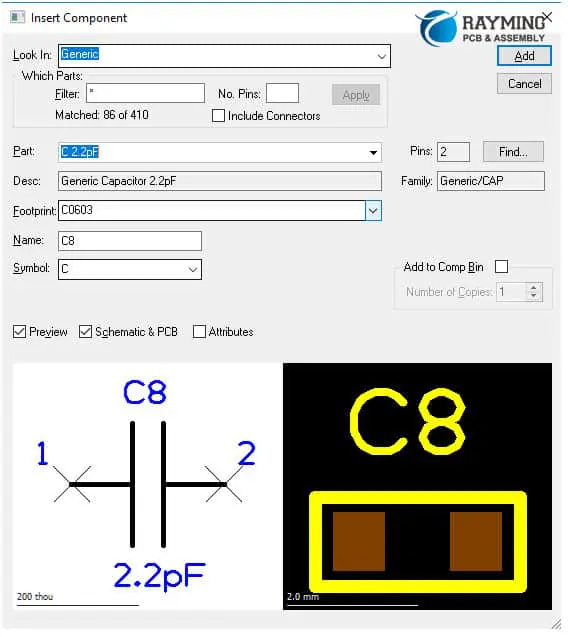

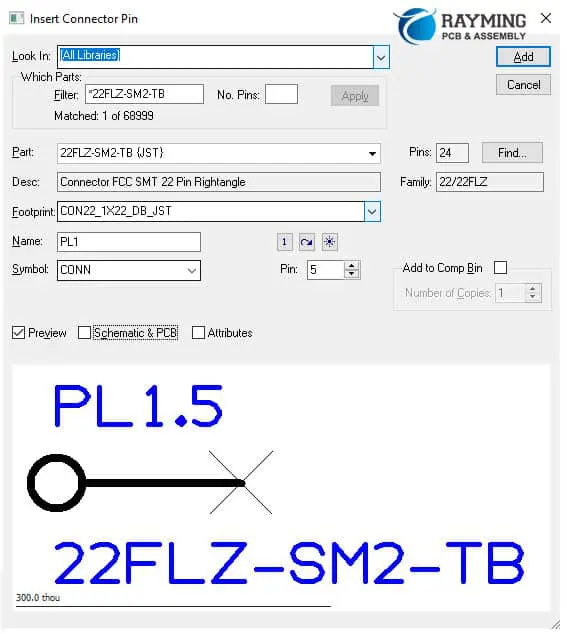

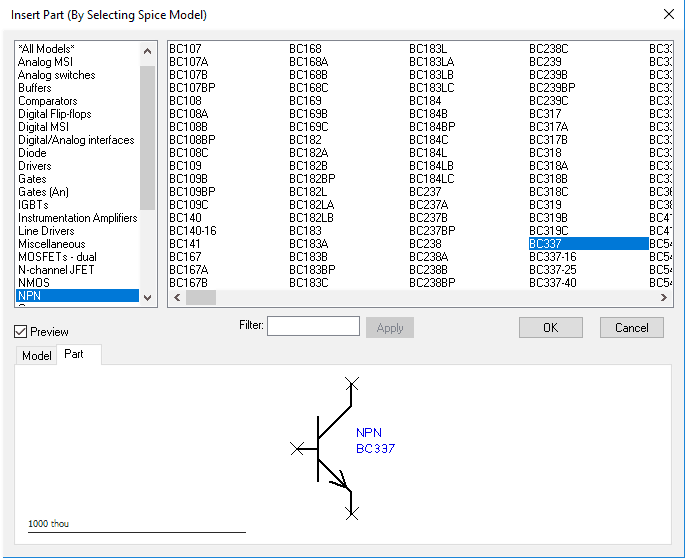

The image above has a total of four columns i.e. Comment, Designator, Footprint, and LCSC Part Number. The Comment is indicating the parts used in the PCBs with its actual values. It describes each component in detail with exact values such as a capacitors C1, C2, C3, and C4 having same values of 0.1uF. However, some of other information must also be catered such as tolerance and voltage allowing capacity etc. Designator is describing the components which are placed at different points. For example, capacitors of values 22pF are placed at points C5, and C6. PCB Footprint is of great importance because the packages in SMD parts are coming in different sizes, and hence the assembling engineer must be knowing which package is going to be best fit in the Printed Circuit Board.

Therefore, the assembly engineer must be aware of the different sizes SMT which are used in the PCB design such as 0603, 0805, and 1206 etc. LCSC Part Number is the column having information for speeding up the process of assembly of PCBs and getting precise results. Each component of the PCB has a unique number through which it is recognized and there is usually a stock of components with each PCB manufacturer. Therefore, this unique component number is very keen in recognition of the component being used and if still there exist any ambiguity then the component unique number might be searched in the library.

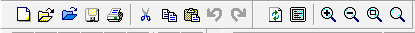

The following image is illustrating the Component number C382097 to be a capacitor having value of 1nF and is to be placed at point C1 on the PCB.

For the purpose of exporting the Bill of Materials from KiCAD tool, you are required to click or go to the script of Arturo’s BOM export. You can easily find it on the web. Download the script which is usually in ZIP form and then unpack it. The image below is illustrating way to acquire the Arturo’s BOM script, downloading, and installation of the script.

After the installation of the script, open it and then click on the option of Export BOM for the specific PCB required. You have to add the BOM script in to the KiCAD PCB file which is opened. From the command window of the KiCAD tool, change the command to %O.csv from the command %O and then click on the generate BOM for its generation. This is going to generate the required BOM which is required for the PCB Assembly process. The figure below is demonstrating the method described above for changing the command and then generation of BOM.

The Generation of Component Placement List from KiCAD Tool

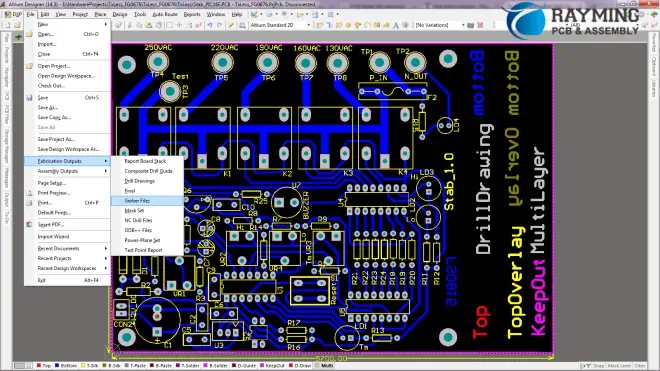

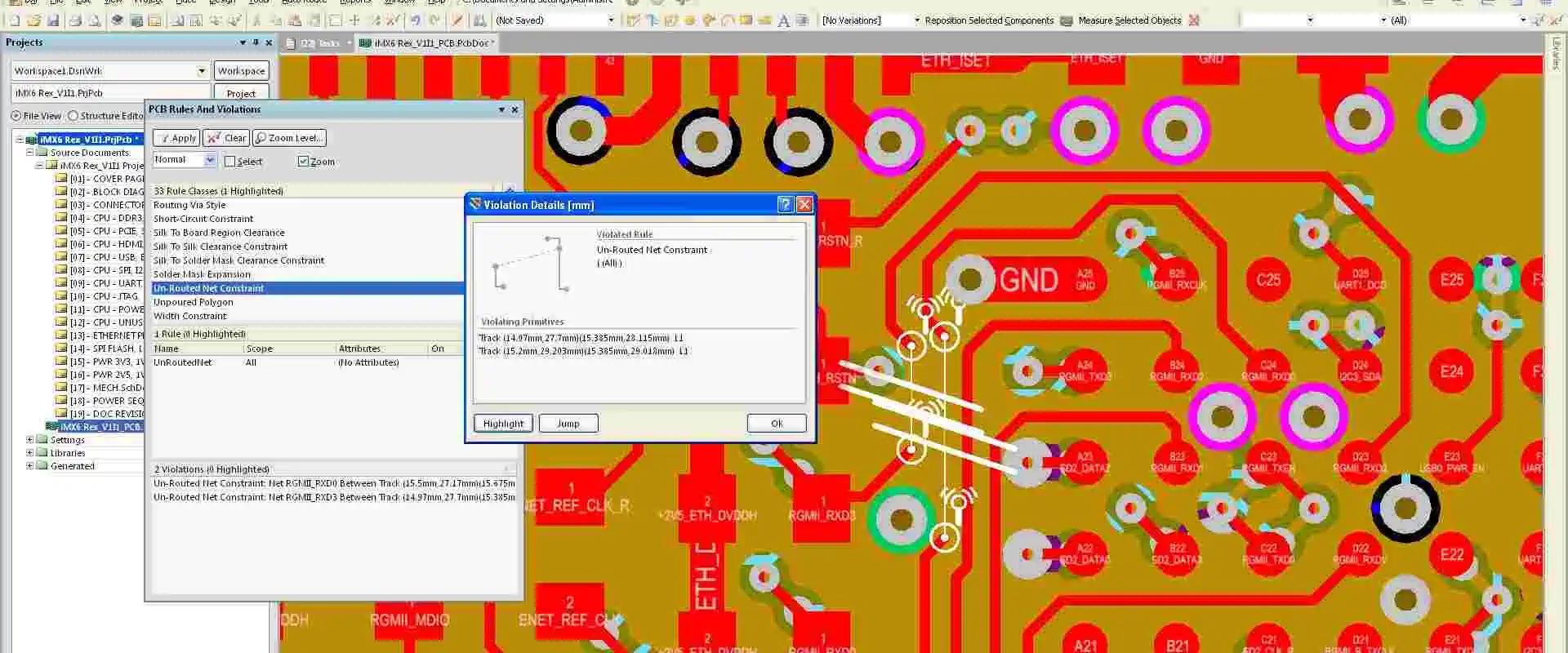

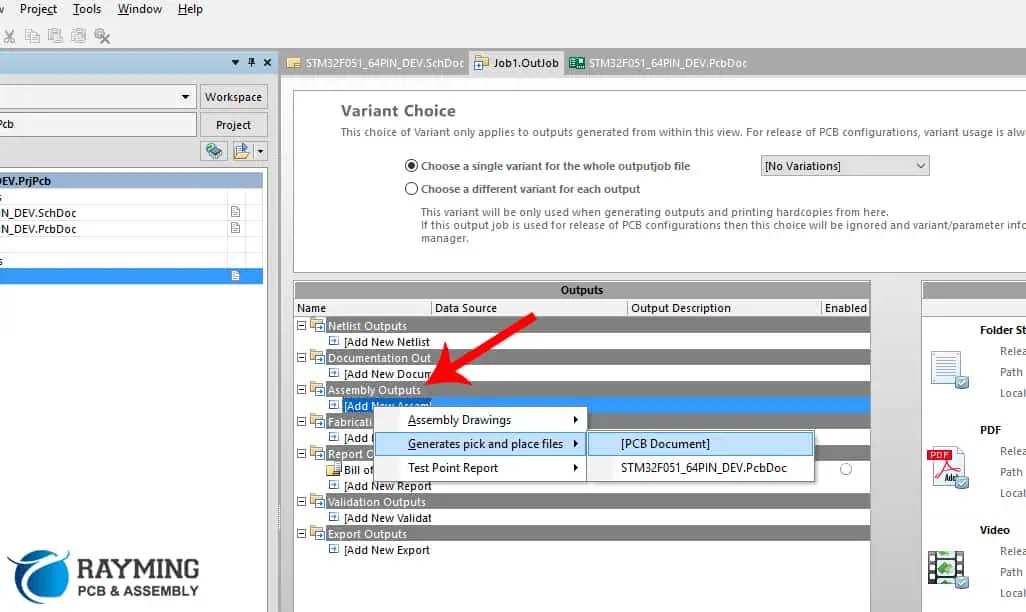

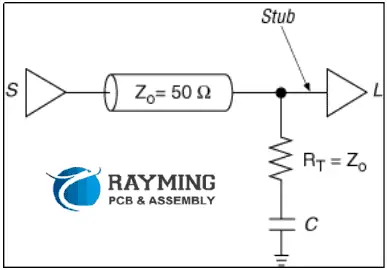

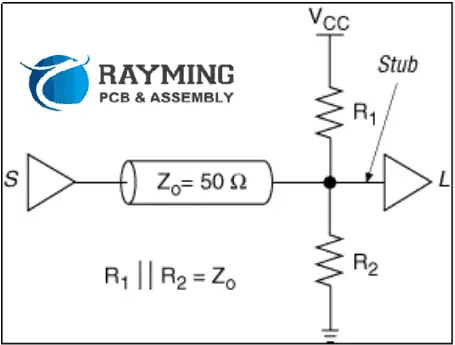

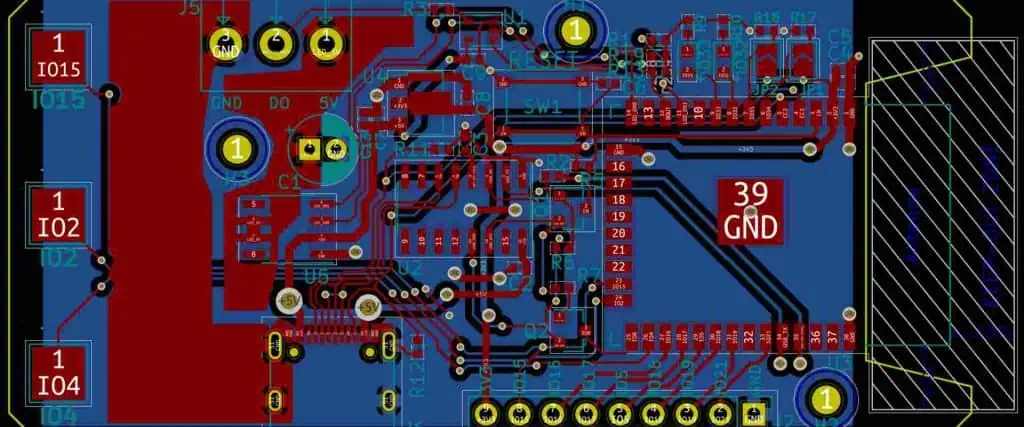

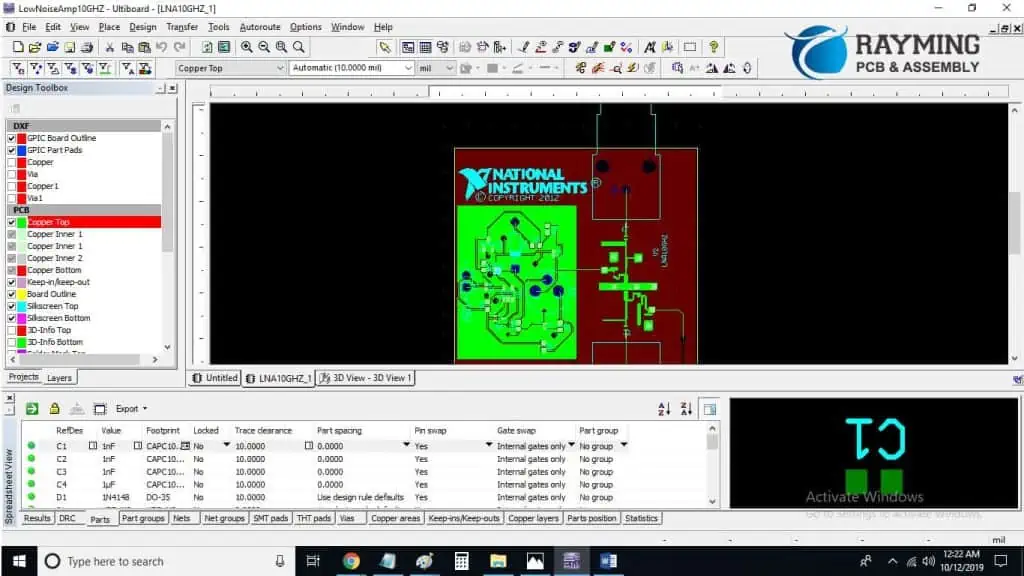

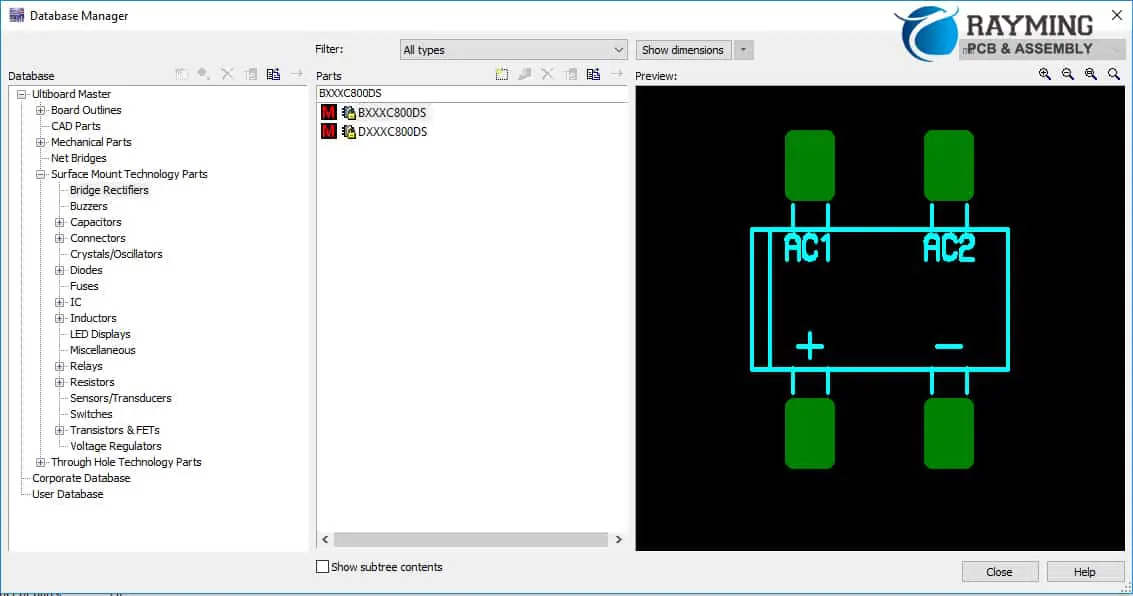

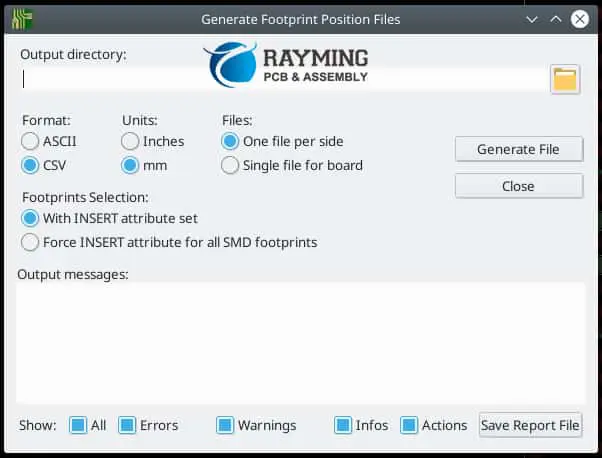

As described earlier that the Component Placement List which is also known as Pick and Place list of the component can also be generated from KiCAD tool. Therefore, for CPL list acquisition, first of all the PCB editor needs to be opened. By clicking on the “File” option in the PCB editor, go to the option “Fabrication Output” and then click on the “Footprint Position”. The footprint position is in .pos format. You have to export the file and then change it with the settings shown in image below.

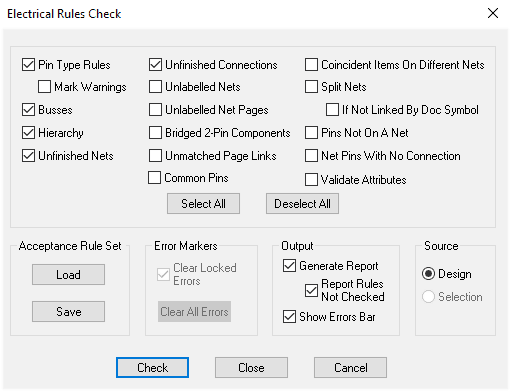

First of all you need to change the format of the file to “.csv”, change the required units in to “mm”, and “One file per side”. After this, you have to select the footprint selection to “with INSERT attribute set”. At the end you have to click on the all options given at bottom of tab i.e. “all, errors, warnings, infos, and actions”. At the end click on “save report file”, however give proper location where the file has to be saved.

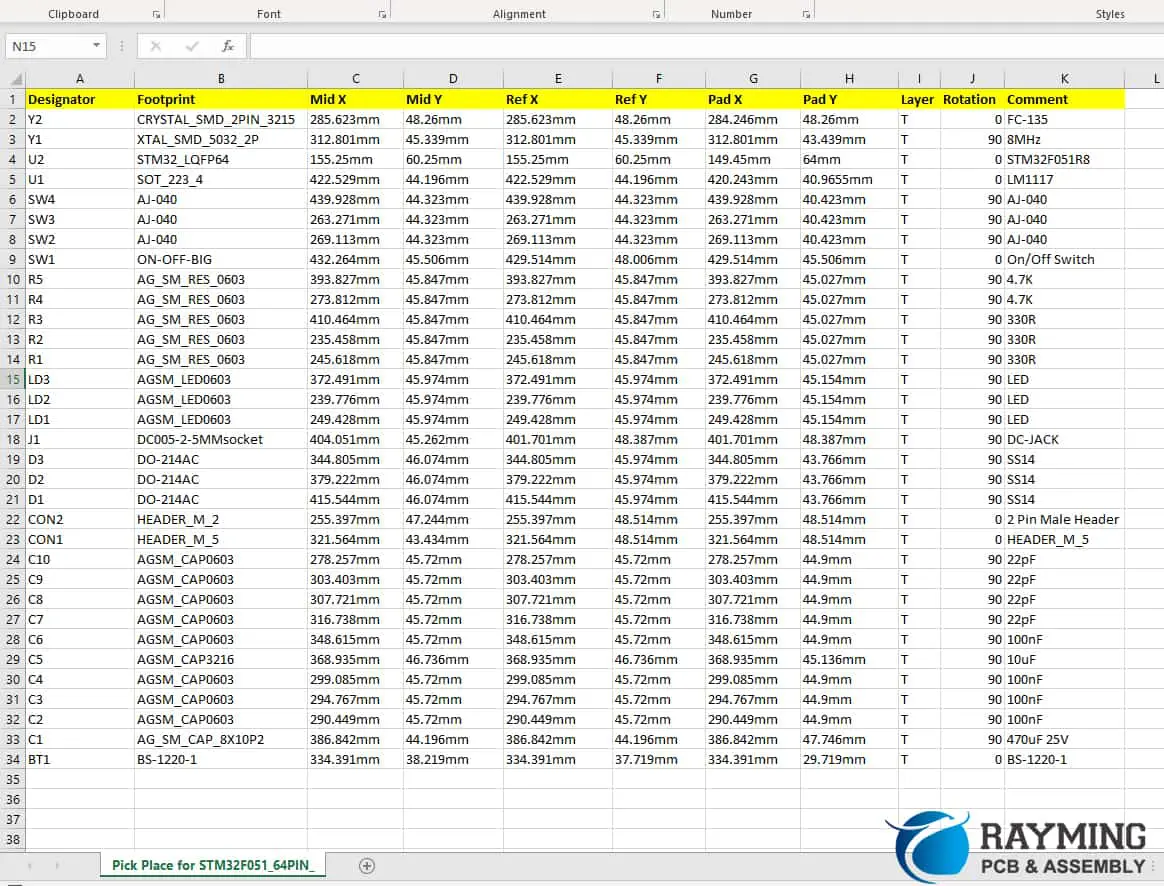

For having a compliance with the RayPCB SMT, you are required to edit the Component Placement List file libreoffice Calc. or excel format. Therefore, for the purpose you are required to do the changes as described below.

First of all you have to ref to the designator of PosX to that fo Mid X PosY to Mid Y Rot to Rotation Side to Layer, before making the export form the KiCAD tool.

After the modification of the header, you will get the file with following format illustrated in image below.

Introduction

KiCAD is a popular open-source Electronics Design Automation (EDA) software suite used for Printed Circuit Board (PCB) design. It provides schematic capture and PCB layout functionality along with various other features for electronics engineers. One of the most useful features of KiCAD is its ability to generate manufacturing output files like centroid files, bill of materials (BOM), Gerber files, etc. These files are essential for PCB fabrication and assembly. In this article, we will focus on the method to generate two key output files from KiCAD – the centroid file and the BOM.

Centroid File

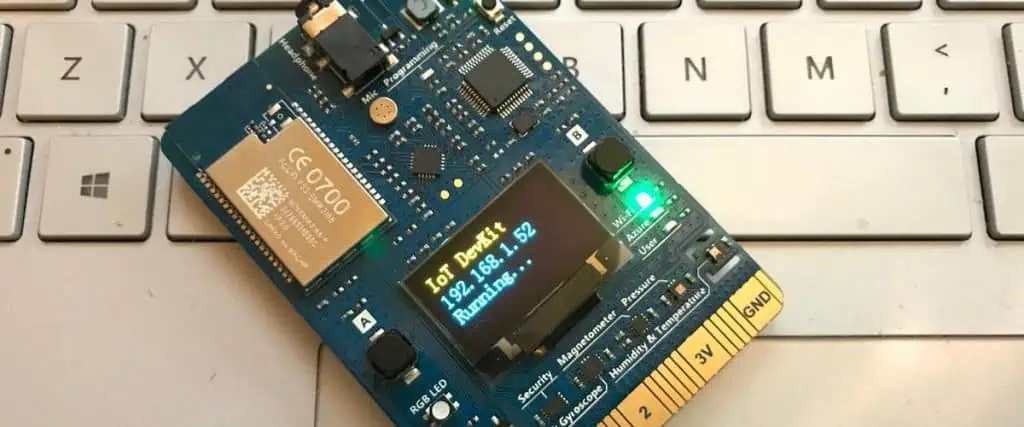

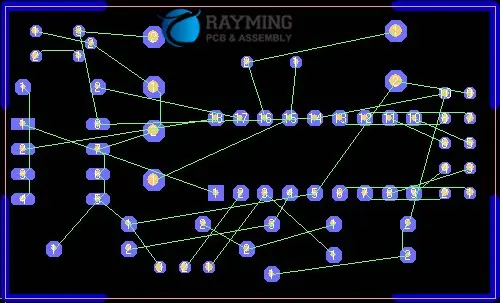

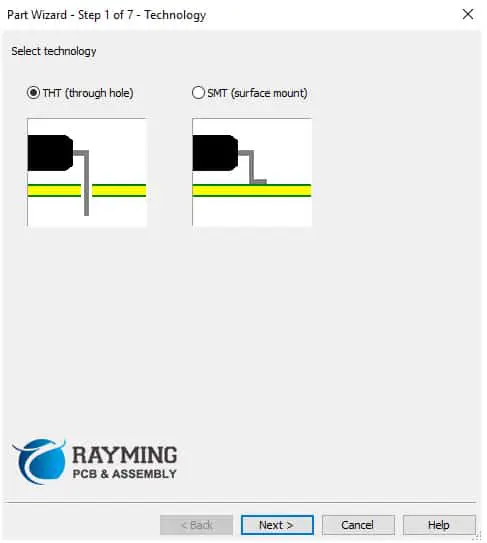

The centroid file provides the center coordinates or centroids of all PCB footprints. It is required by the pick and place machine to accurately place components on the PCB board during assembly. Here are the steps to generate the centroid file in KiCAD:

1. Creating Footprints with 3D Models

The first step is to assign 3D models to all the footprints used in the PCB layout. The centroid data is extracted from these 3D models. KiCAD includes many pre-defined 3D models and you can also create custom models.

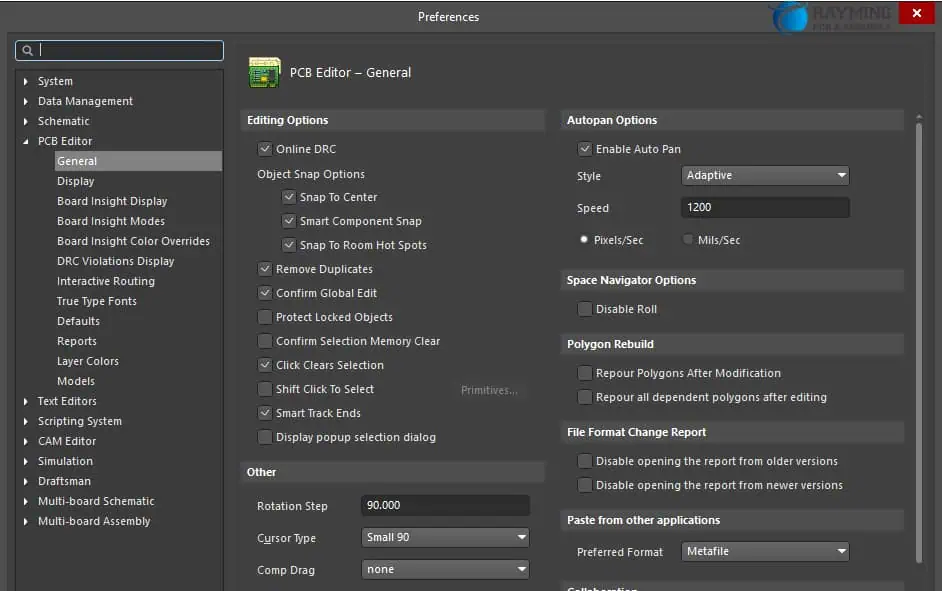

2. Enabling 3D Viewer

The 3D viewer must be enabled in PCBNew to render the board with 3D models for generating the centroid file. This can be done by going to Preferences > 3D Viewer and checking Enable 3D Viewer.

3. Running the 3D Generator

Go to Tools > Generate Fabrication Output. This will open up the fabrication output job editor. Under the General Options tab, enable the following:

- Force recreate files

- Use complete suffix

- Use 3D models

- Generate centroid info

This will regenerate all the manufacturing files including the centroid data when the job is run.

4. Executing the Job

Click on the Generate button and the fabrication job will be executed. This will generate centroid info in a file named <filename>_centroid_info.csv along with other fabrication outputs.

The centroid file can be found under the main project folder. It contains a list of all footprints along with their reference designator, center X, Y coordinates and rotation angle. These coordinates should match the 3D models visible when the 3D viewer is enabled.

Bill of Materials (BOM)

The BOM or bill of materials is a list of all the components used in a PCB along with key information like reference designator, description, quantity, etc. The BOM acts as a shopping list for purchasing components for production. The following steps describe how to generate a BOM from KiCAD schematics:

1. Associating Components with Schematic Symbols

For each component in the schematic, make sure to associate it with a schematic symbol and provide a unique reference designator. This information will get populated in the BOM.

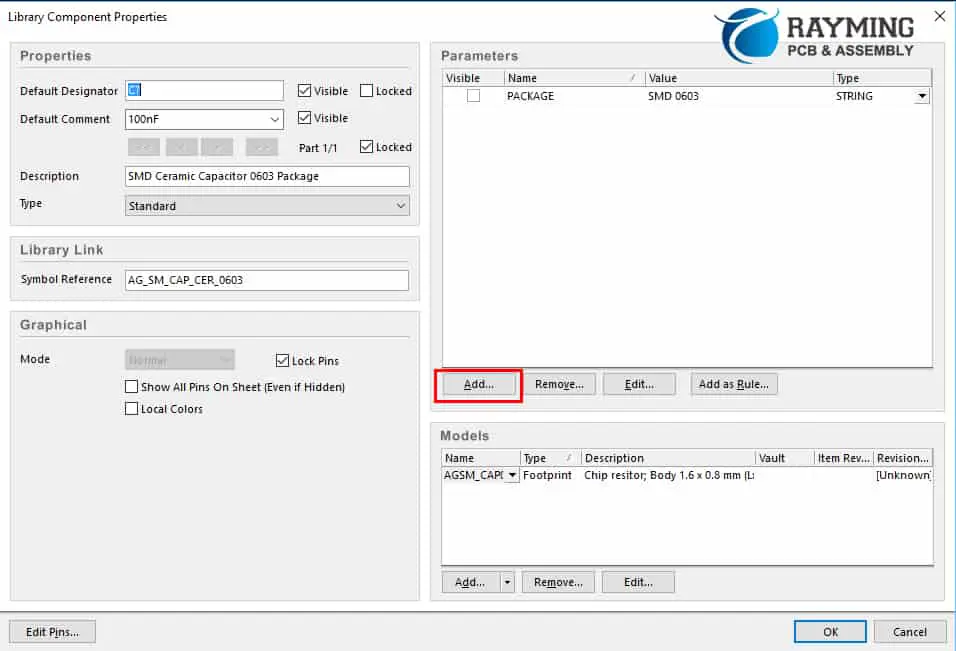

2. Including Part Information

Add complete part information like manufacturer name, part number, description, etc. for each component in the schematic. This data can be entered in the component’s properties window.

3. Assigning Field Names

KiCAD allows mapping the part fields like description, part number, etc. to specific column headers in the BOM. This can be configured in the schematic editor preferences.

4. Generating Netlist

Before generating BOM, you need to create a netlist to synchronize the schematic and PCB. Go to Tools > Generate Netlist to create the netlist file.

5. Using Component Class Dialog

The component class dialog in PCBNew is used to classify components into various types like integrated circuits, resistors, capacitors etc. This classification can be used to group components in the BOM.

6. Generating BOM

Finally, go to Tools > Generate Bill of Materials to create the BOM. This will generate a .csv file containing the reference, quantity, description, part number and other fields for all components.

The BOM can be customized further by editing the template or XSLT stylesheet used for BOM generation. Fields can be added, removed or rearranged as per requirements.

Additional Points

Here are some additional points to keep in mind while generating BOM and centroid files:

- The fabrication output generator provides many options to customize the outputs as per board house requirements.

- The Reference Reference column can be used in the BOM to cross-reference components from schematic to PCB.

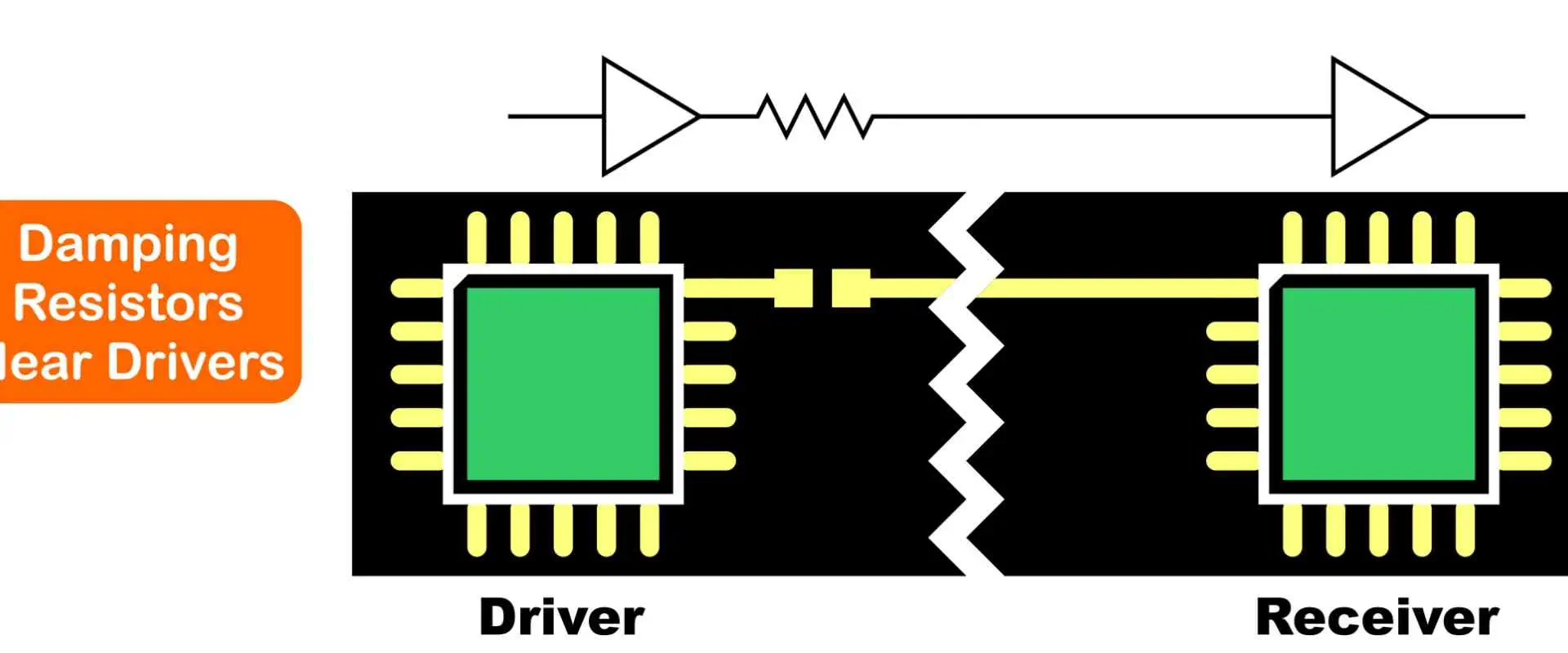

- The position and rotation column in BOM provides placement info that can be used during assembly in combination with the centroid file.

- Multiple BOMs can be generated with different grouping and filtering criteria.

- The component grouping feature is useful for organizing BOM by component types.

- Scripting can be used to automate running the fabrication output generator for quick BOM/centroid file creation.

Conclusion

Generating manufacturing files like BOM and centroid data is crucial before sending a PCB design for fabrication and assembly. KiCAD’s fabrication output generator provides an efficient one-step solution to create these files from the PCB projects. Configuring the right options and customizing the output templates allows generating high quality BOM and centroid files that can be readily used by PCB manufacturers. This automated documentation saves significant amount of time and effort while also minimizing errors during the manufacturing process.

Frequently Asked Questions

Q1. What is the importance of a centroid file?

A1. The centroid file provides the center point coordinates of all PCB footprints which are required for accurate component placement by pick and place machines during assembly.

Q2. Can BOM be generated without creating a PCB layout?

A2. Yes, BOM can be created directly from the schematics before PCB layout by using the Generate Bill of Materials tool in EESchema.

Q3. What is the use of component grouping in BOM generation?

A3. Component grouping allows classifying components into categories like ICs, resistors, capacitors etc. This groups components in the BOM making it easier to read and analyze.

Q4. How can the BOM be customized in KiCAD?

A4. BOM can be customized by editing the BOM template and XSLT stylesheet used for generation. This allows changing fields, ordering, grouping etc. as per requirements.

Q5. Is it possible to generate multiple centroid files for different PCB assemblies?

A5. Yes, multiple centroid files can be generated by creating assemblies of boards and footprints. The 3D generator can then output separate centroid files for each assembly.