In the realm of high-speed digital design, signal and power integrity have become critical factors that can make or break a system’s performance. As clock frequencies increase and signal rise times decrease, the need for a thorough understanding of signal and power integrity fundamentals becomes paramount. This article delves into the key concepts, challenges, and best practices associated with maintaining signal and power integrity in high-speed designs.

Understanding Signal Integrity

What is Signal Integrity?

Signal integrity refers to the quality of an electrical signal as it travels through a transmission line or a printed circuit board (PCB). In high-speed designs, maintaining signal integrity ensures that digital signals arrive at their destination with sufficient quality to be correctly interpreted by the receiving device.

Key Signal Integrity Challenges

High-speed designs face several signal integrity challenges, including:

- Reflections

- Crosstalk

- Electromagnetic interference (EMI)

- Jitter

- Attenuation

- Impedance discontinuities

Transmission Line Theory

Understanding transmission line theory is crucial for addressing signal integrity issues. Key concepts include:

- Characteristic impedance

- Propagation delay

- Reflection coefficient

- Time domain reflectometry (TDR)

Signal Integrity Analysis Techniques

Time Domain Analysis

Time domain analysis involves examining signal waveforms over time. Key metrics include:

- Rise time

- Fall time

- Overshoot

- Undershoot

- Settling time

Frequency Domain Analysis

Frequency domain analysis examines signals in terms of their frequency components. Important concepts include:

- Bandwidth

- Nyquist frequency

- Harmonics

- S-parameters

Eye Diagram Analysis

Eye diagrams provide a comprehensive view of signal quality. Key parameters measured using eye diagrams include:

| Parameter | Description |

| Eye height | Vertical opening of the eye |

| Eye width | Horizontal opening of the eye |

| Jitter | Timing variations in the signal |

| Bit error rate (BER) | Probability of bit errors |

Signal Integrity Design Techniques

Impedance Matching

Proper impedance matching is crucial for minimizing reflections. Techniques include:

- Series termination

- Parallel termination

- Differential pair routing

Crosstalk Mitigation

To reduce crosstalk, consider the following strategies:

- Increasing spacing between traces

- Using guard traces

- Implementing orthogonal routing on adjacent layers

EMI Reduction

Minimize electromagnetic interference through:

- Proper stackup design

- Use of ground planes

- Implementing EMI shields

Jitter Management

Reduce jitter in high-speed designs by:

- Optimizing clock distribution networks

- Using low-jitter oscillators

- Implementing proper power supply decoupling

Understanding Power Integrity

What is Power Integrity?

Power integrity refers to the quality of the power distribution network (PDN) in a system. It ensures that all components receive clean, stable power at the required voltage levels.

Key Power Integrity Challenges

High-speed designs face several power integrity challenges, including:

- Voltage drops

- Power supply noise

- Switching noise (dI/dt)

- Resonances in the PDN

- Ground bounce

Power Distribution Network (PDN) Components

A typical PDN consists of:

- Voltage regulator modules (VRMs)

- Bulk capacitors

- Decoupling capacitors

- Power planes

- Vias and traces

Power Integrity Analysis Techniques

DC Analysis

DC analysis focuses on static voltage drops and current distribution. Key metrics include:

- IR drop

- Current density

- Power consumption

AC Analysis

AC analysis examines the dynamic behavior of the PDN. Important concepts include:

- Target impedance

- PDN impedance profile

- Self-resonant frequency of capacitors

Time Domain Analysis

Time domain analysis for power integrity involves examining:

- Voltage ripple

- Transient response

- Simultaneous switching noise (SSN)

Power Integrity Design Techniques

Decoupling Capacitor Selection and Placement

Proper selection and placement of decoupling capacitors is crucial for maintaining power integrity. Consider:

- Capacitor values and types

- Placement strategy (local vs. global decoupling)

- Effective frequency range of capacitors

| Capacitor Type | Typical Value Range | Effective Frequency Range |

| Bulk | 10 µF – 1000 µF | < 1 MHz |

| MLCC | 0.1 µF – 10 µF | 1 MHz – 100 MHz |

| High-frequency | 1 nF – 0.1 µF | > 100 MHz |

Power Plane Design

Optimize power plane design by:

- Using solid power planes

- Implementing proper stackup design

- Minimizing splits in power planes

Voltage Regulator Module (VRM) Design

Consider the following factors in VRM design:

- Output voltage accuracy

- Load regulation

- Transient response

- Efficiency

Ground Bounce Mitigation

Reduce ground bounce through:

- Proper stackup design

- Use of multiple ground vias

- Implementing ground planes

Signal and Power Integrity Co-Design

Importance of Co-Design

Signal and power integrity are closely interrelated in high-speed designs. Co-design considerations include:

- Return path discontinuities

- Simultaneous switching noise (SSN)

- Power supply induced jitter

Design Tradeoffs

Balancing signal and power integrity often involves tradeoffs:

- Trace width vs. impedance control

- Decoupling vs. signal routing space

- Power plane splits vs. return path continuity

Simulation and Measurement Techniques

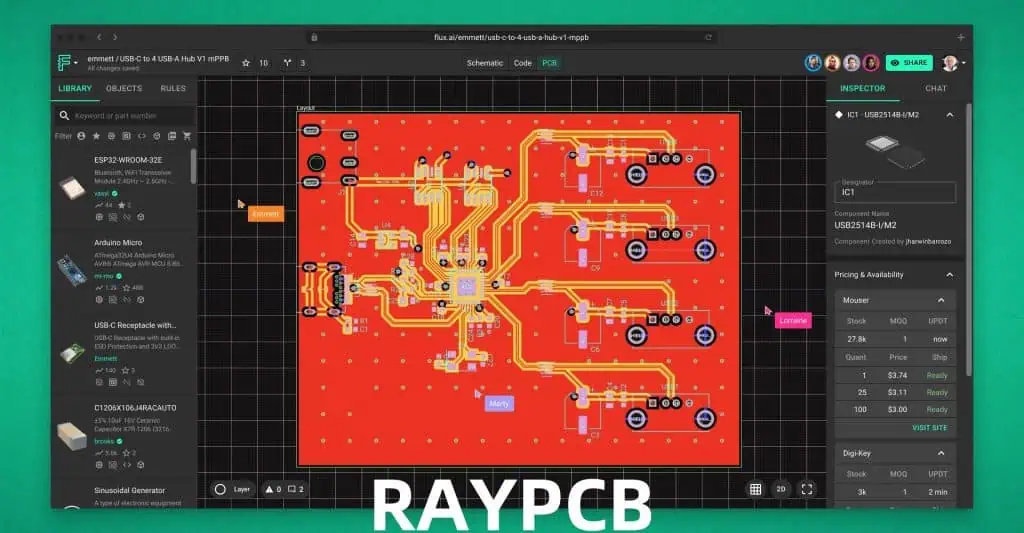

Simulation Tools

Various simulation tools are available for signal and power integrity analysis:

- SPICE-based circuit simulators

- 3D electromagnetic field solvers

- System-level simulators

Measurement Equipment

Key measurement equipment for signal and power integrity include:

- High-speed oscilloscopes

- Vector network analyzers (VNAs)

- Time domain reflectometers (TDRs)

- Near-field EMI scanners

Design for Signal and Power Integrity

PCB Stackup Design

Proper PCB stackup design is crucial for both signal and power integrity:

- Use an even number of layers for symmetry

- Alternate signal and plane layers

- Keep high-speed signals close to reference planes

Component Placement and Routing

Optimize component placement and routing for signal and power integrity:

- Place decoupling capacitors close to ICs

- Minimize trace length for critical signals

- Use star routing for clock distribution

Design Rules and Constraints

Implement design rules and constraints to ensure signal and power integrity:

- Set maximum trace length limits

- Define impedance-controlled routing rules

- Establish power integrity constraints (e.g., target impedance)

Advanced Topics in Signal and Power Integrity

High-Speed Serial Links

Design considerations for high-speed serial links include:

- Equalization techniques

- Clock and data recovery (CDR)

- Channel modeling and simulation

3D IC and Package Design

Signal and power integrity challenges in 3D IC and package design:

- Through-silicon vias (TSVs)

- Interposer design

- Package-level power distribution

Signal and Power Integrity for RF and Mixed-Signal Designs

Special considerations for RF and mixed-signal designs:

- Isolation between analog and digital domains

- Substrate noise coupling

- Low-noise power supply design

Case Studies

Case Study 1: DDR4 Memory Interface

A designer optimized a DDR4 memory interface for signal and power integrity:

- Implemented length-matched differential pairs

- Used IBIS-AMI models for simulation

- Optimized PDN for target impedance of 1 mΩ up to 1 GHz

Results:

- Achieved data rates of 3200 MT/s with acceptable eye margin

- Reduced power supply noise by 30% compared to previous design

Case Study 2: 56 Gbps PAM-4 SerDes

A team designed a 56 Gbps PAM-4 SerDes with focus on signal and power integrity:

- Implemented continuous-time linear equalization (CTLE)

- Used decision feedback equalization (DFE)

- Optimized power delivery network for low noise

Results:

- Achieved bit error rate (BER) of 10^-15 at 56 Gbps

- Reduced total jitter by 40% compared to previous generation

Conclusion

Signal and power integrity are foundational aspects of high-speed digital design. As data rates continue to increase and voltages decrease, the challenges associated with maintaining signal and power integrity become more pronounced. By understanding the fundamental concepts, applying best practices, and utilizing advanced simulation and measurement techniques, designers can create robust, high-performance systems that meet the demands of modern electronics.

The field of signal and power integrity is constantly evolving, with new challenges emerging as technology advances. Staying current with the latest techniques, tools, and industry standards is crucial for engineers working in this domain. By carefully considering signal and power integrity throughout the design process, from initial concept to final verification, designers can create systems that push the boundaries of speed and performance while maintaining reliability and signal quality.

Frequently Asked Questions (FAQ)

Q1: What is the difference between signal integrity and power integrity?

While both signal integrity and power integrity are crucial for high-speed designs, they focus on different aspects of the system:

Signal Integrity:

- Focuses on the quality of individual signals

- Deals with issues like reflections, crosstalk, and jitter

- Aims to ensure signals are correctly interpreted at the receiver

Power Integrity:

- Focuses on the quality of the power distribution network (PDN)

- Deals with issues like voltage drops, power supply noise, and resonances

- Aims to ensure clean, stable power delivery to all components

While distinct, signal and power integrity are closely interrelated, as power integrity issues can significantly impact signal integrity, and vice versa.

Q2: How does increasing frequency affect signal and power integrity?

As frequency increases, several challenges become more pronounced:

- Transmission line effects become significant, leading to more reflections and impedance discontinuities

- Crosstalk between adjacent traces increases due to stronger electromagnetic coupling

- Skin effect and dielectric losses increase, causing more signal attenuation

- Power distribution network (PDN) impedance becomes more critical at higher frequencies

- Electromagnetic interference (EMI) issues become more severe

- Jitter and timing margins become tighter, requiring more precise design

To address these challenges, designers must employ more advanced techniques, such as impedance-controlled routing, proper stackup design, and careful power integrity management.

Q3: What are some common tools and techniques for measuring signal and power integrity?

Common tools and techniques include:

For Signal Integrity:

- High-speed oscilloscopes for time-domain analysis

- Vector Network Analyzers (VNAs) for S-parameter measurements

- Time Domain Reflectometers (TDRs) for impedance profiling

- Bit Error Rate Testers (BERTs) for system-level performance evaluation

- Eye diagram analyzers for comprehensive signal quality assessment

For Power Integrity:

- DC power analyzers for static voltage and current measurements

- AC voltage and current probes for dynamic measurements

- Spectrum analyzers for frequency-domain noise analysis

- Impedance analyzers for PDN impedance profiling

- Near-field EMI scanners for identifying noise sources on the PCB

Additionally, various simulation tools are used for both signal and power integrity analysis, including SPICE-based circuit simulators, 3D electromagnetic field solvers, and system-level simulators.

Q4: How do you determine the appropriate decoupling capacitor strategy for a high-speed design?

Determining the appropriate decoupling capacitor strategy involves several steps:

- Estimate the target impedance of the PDN based on voltage tolerance and current draw

- Analyze the PDN impedance profile without decoupling capacitors

- Select a range of capacitor values to cover the frequency range of interest

- Determine the number of each capacitor value needed to meet the target impedance

- Place bulk capacitors near voltage regulators for low-frequency decoupling

- Place smaller value capacitors near ICs for high-frequency decoupling

- Use electromagnetic simulation to verify the effectiveness of the decoupling strategy

- Iterate and optimize based on simulation results and physical constraints

The goal is to maintain the PDN impedance below the target impedance across the entire frequency range of interest, typically from DC to 5-10 times the highest clock frequency in the system.

Q5: What are some key considerations for maintaining signal and power integrity in high-speed differential pairs?

Key considerations for high-speed differential pairs include:

- Impedance matching: Ensure the differential impedance matches the target value (typically 85-100 ohms)

- Length matching: Keep the length of each trace in the pair closely matched (within 5-10 mils)

- Coupling: Maintain tight coupling between the traces to improve common-mode noise rejection

- Symmetry: Keep the environment around each trace as symmetrical as possible

- Transitions: Minimize impedance discontinuities at layer transitions and component connections

- Crosstalk: Maintain adequate spacing from other differential pairs and single-ended signals

- Return path: Ensure a continuous return path, preferably a solid ground plane

- Termination: Use proper differential termination techniques to minimize reflections

- Power integrity: Provide clean power and ground references to minimize power-induced jitter

- Routing: Use curved or 45-degree routing instead of 90-degree bends to maintain impedance control

By carefully considering these factors, designers can create high-speed differential pairs that maintain signal integrity while minimizing electromagnetic interference and susceptibility to power integrity issues.