Introduction

Package on Package (POP) is an integrated circuit packaging technique used in electronics manufacturing where packaged semiconductor devices are stacked vertically using solder balls. This enables higher component density and improves electrical performance for advanced PCB designs. In this article, we will explore the fundamentals of POP technology, its assembly process, advantages, limitations, applications and future trends.

Overview of POP

POP involves integrating two or more completely packaged devices into a single composite component unit by stacking them vertically. Some key points:

- Each device is separately packaged first before POP assembly.

- Devices are interconnected using solder balls or bumps.

- The bottom device is called the ‘base package’.

- The top stacked package is called the ‘top package’.

- Interposer may be used between packages for re-routing.

- Entire POP assembly is treated as a single packaged component.

- Also referred to as package-on-package (PoP) or package-over-package.

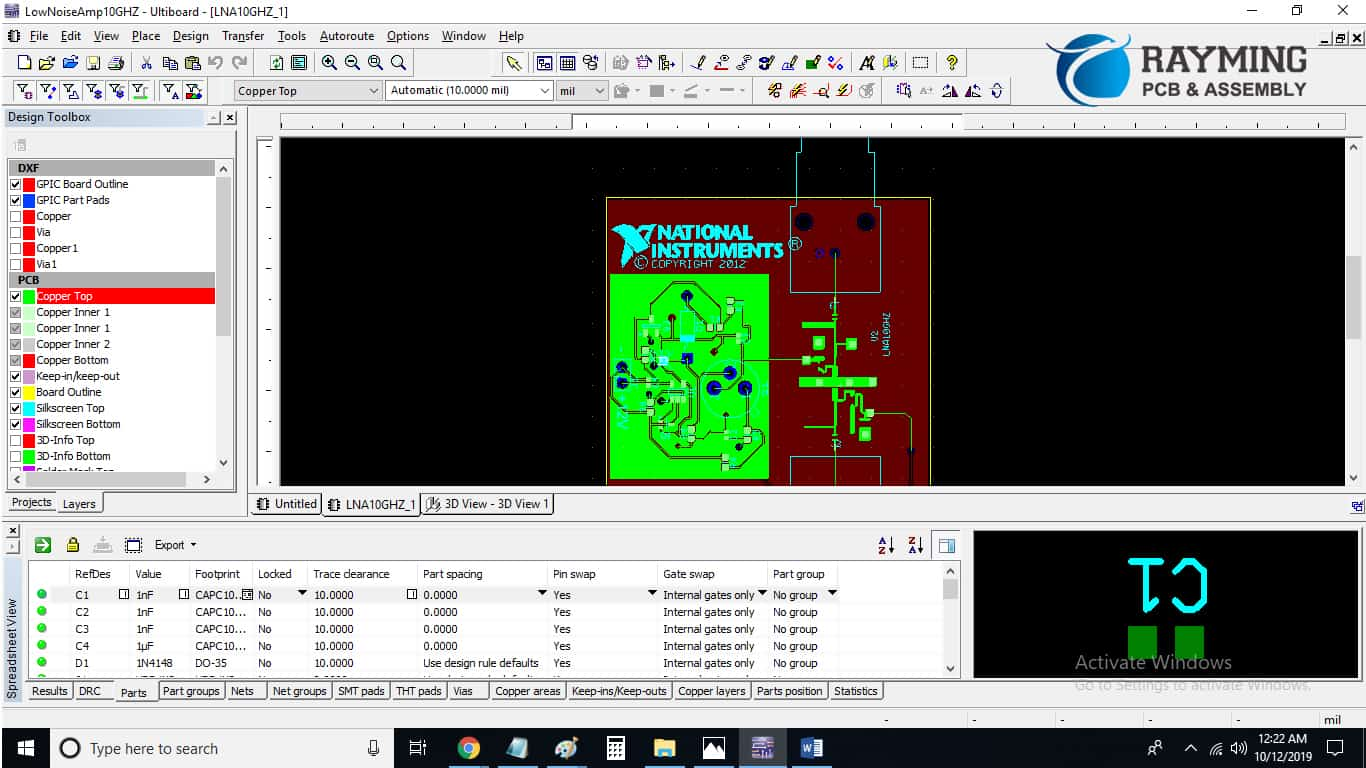

POP configuration showing stacked packages interconnected by solder balls.

Why POP is Used?

Some key benefits driving the adoption of POP technology:

- Allows vertical stacking of ICs for increased component density on PCB.

- Enables integrating disparate technologies like memory, processors, sensors etc.

- Improves electrical performance through double-sided interconnections.

- Provides flexibility for modular designs by stacking known good packaged devices.

- Simplifies PCB routing by reducing number of components required on board.

- Allows customized configurations suited for target application.

- Reduces the overall footprint and height compared to side-by-side placement.

POP Components

POP assembly combines two main types of packaged components:

1. Base Package

- Typically contains high pin count device like application processor.

- Provides mechanical support for POP structure.

- Made with standard packages like FBGA, PBGA, LGA etc.

- Contains high density of solder balls or bumps on top side.

2. Top Package

- Usually a memory device like DRAM, flash etc.

- Comes in packages like TSOP, CSP or wafer-level CSP (WLCSP).

- Has solder balls only on bottom side.

- Smaller in size than base package.

Interposer

- Optional substrate placed between base and top package.

- Facilitates re-routing of I/O connections.

- Used to optimize pad layout or enable high density ball grid array (BGA).

POP Manufacturing Process

POP assembly involves the following key manufacturing stages:

1. Sourcing Packaged Components

- Obtain fully packaged and tested base and top devices.

- Components must be compatible for stacking and interconnections.

2. Applying Solder Paste

- Dispense solder paste on base package substrates using stencil.

- For some assemblies, paste may also be applied on top package.

3. Placing Base Package

- Mount base package on PCB using standard SMT process.

- May involve reflow soldering to secure base package.

4. Attaching Top Package

- Position top package accurately over base package.

- Orient top package solder balls with base package pads.

5. POP Reflow

- Reflow solder entire POP assembly to form solder joints.

- Special oven profiles are used to manage thermal stresses.

6. Underfill Dispensing

- Wick underfill material via capillary action to fill gap between packages.

- Underfill provides mechanical stability and prevents stress on joints.

7. Conformal Coating

- Apply protective encapsulating material over entire assembly.

- Improves reliability and environmental resistance.

This completes the POP manufacturing process. The components are then put through inspection, programming, testing etc. based on specific product requirements.

POP Design Considerations

Some POP design factors to consider during PCB layout and assembly process planning:

Package Selection

- Height of stacked packages to meet overall height constraints.

- Compatible ball pitch, materials and CTE between packages.

- Solder ball alloy suited to reflow process.

- Underfill fill requirements based on gap between packages.

Electrical Design

- Electrical connectivity through solder balls between packages.

- Minimal stubs lengths for signal routing.

- Matched impedances for high speed signals.

- Power, ground and thermal management.

PCB Land Pattern Design

- Pad shape and size to suit BGA packages.

- Sufficient clearance between pads and surrounding tracks/vias.

- Non-solder mask defined pads.

Solder Paste Stencil Design

- Stencil thickness, aperture size, shape for optimum paste release.

- Step down thickness in stencil for base package pads.

Process Considerations

- Compatible reflow profile to solder both packages.

- Underfill dispensing process window.

- Balanced placement to minimize warpage.

Advantages of POP

The major benefits provided by Package on Package technology are:

Increased Density

- Stacking components vertically conserves PCB area.

- Reduces length of interconnects between packages.

Enhanced Electrical Performance

- Double-sided interconnects minimize parasitic inductances.

- Wider power/ground connections improve current delivery.

Lower Height Profile

- POP provides about 60% height reduction compared to side-by-side placement.

- Lower profile critical for thin and compact product designs.

Design Flexibility

- Allows integration of disparate package types.

- Custom configurations possible by mixing components.

Improved Manufacturability

- Leverages existing SMT assembly process.

- Known good pre-tested packages simplify process control.

Cost Savings

- Eliminates SiP substrate, interconnect layers.

- Shared reflow process reduces costs.

Disadvantages and Limitations

Some drawbacks and challenges of using POP approach:

Thermo-mechanical Stresses

- CTE mismatch between packages induces stresses during thermal cycling.

- Can affect long term reliability of solder joints.

Narrow Process Window

- Reflow profile optimization is critical for good joint formation.

- Underfill voiding can occur due to improper dispense process.

Warpage Control

- Unbalanced stacking leads to significant warpage.

- Requires symmetrical design and placement during assembly.

Design Constraints

- Restricts pin assignments, placement and routing on PCB.

- Requires extensive modeling and analysis.

Inspectability

- X-ray inspection capability needed to detect defects under top package.

- Fault isolation challenging in stacked configuration.

POP Applications

Some common application areas where POP technology provides benefits:

Smartphones

- Memory+processor stacking enables powerful smartphones.

- Allows integrating memory, power management, RF and sensors.

Wearable Devices

- Miniaturization for compact wearable product form factors.

- Lightweight flexible POP solutions ideal for wearables.

Internet of Things (IoT)

- Small footprint and height critical for many IoT devices.

- Custom stacking combinations possible for specific devices.

High Density Interconnects

- Doubled interconnections density compared to peripheral arrays.

- Well suited for processors requiring high bandwidth memory.

- Rugged POP packages able to withstand temperature cycling.

- Suitable for engine control units and in-vehicle infotainment.

The Future of POP

Some emerging trends and developments in POP packaging technology:

- Hybrid POP configurations integrating passives, sensors along with active ICs using fan-out wafer level packaging.

- Development of ultra-thin wafer level CSPs as top package for slimmer POP.

- Utilization of 2.5D and 3D silicon interposers with fine-pitch interconnects.

- Adoption of through mold vias (TMV) for signal and power delivery through package substrate.

- Flip-chip underfill process improvements to enable ultra-fine pitch POP scaling.

- Novel conductive adhesives like anisotropic conductive films (ACF) as interconnect material.

- Wafer-on-Wafer (WoW) integration for direct device-to-device fine pitch interconnections.

- Applications in high performance computing and networking equipment.

Conclusion

Package-on-Package represents an exciting packaging innovation that enables continued miniaturization and performance scaling of electronic systems through vertical stacking. With its advantages in density, electrical performance and design flexibility, POP will continue to find increased applicability in space-constrained mobile devices, wearables, IoT as well as high performance designs. Ongoing research and developments are focused on pushing the limits further in terms of interconnect density, stack height, thermal management and manufacturability. As semiconductor integration advances, POP promises to provide an ideal platform for heterogeneous integration of multiple dies and components.

FAQs

- How is POP different from package in package (PiP) approach?

In POP, electronic packages are stacked one over the other. In PiP, one package is placed inside another larger package before interconnecting.

- What interconnect materials can be used for POP assembly?

Besides solder balls, conductive adhesives like anisotropic conductive films (ACF) and anisotropic conductive pastes (ACP) are also suitable POP interconnects.

- Does POP eliminate the need for SiP and multichip modules?

POP provides an alternative by directly stacking known good pre-packaged components. However, SiP and MCM are still used when custom or incompatible devices need to be integrated.

- What causes warpage in POP assembly and how is it controlled?

Unbalanced thermal expansion between differently sized top and bottom packages induces warpage. Careful package selection, symmetrical placement and substrate stiffening help reduce warpage.

- How does thermal management differ for POP compared to conventional PCB assembly?

Concentrated heat density requires effective heat spreading to packages. Thermal vias, large ground pads and heat slugs are commonly used techniques.