Introduction

The Xilinx XA Spartan-7 Automotive (XA) FPGA family brings low-power programmable logic to next-generation vehicle systems. Within this family, the XA7A75T-1CSG324Q provides a balanced mix of density, features, and I/O for ADAS, infotainment, connectivity, and other automotive applications.

In this article, we will take a technical deep dive into the XA7A75T FPGA to understand its capabilities, architecture, available resources, and benefits for automotive use cases. We’ll explore the data sheet specifications and configuration options that enable successful deployment of this FPGA.

XA7A75T Overview

The Xilinx XA7A75T sits in the middle of the XA Spartan-7 lineup with these high-level characteristics:

- 75K logic cells

- 5.3Mb block RAM

- 240 DSP slices

- PCIe x1, Gigabit Ethernet blocks

- 324 user I/O pins

- 7.5 x 7.5 mm, 0.8mm pitch FC-BG484 package

- Wide variety of automotive I/O standards

- Power optimized at 0.85W typical consumption

These resources provide ample density for feature-rich automotive systems, balanced with restraints on cost and power consumption. The integrated PCIe, Ethernet, memory, and DSP blocks accelerate key functions while minimizing FPGA resource usage.

FPGA Logic Cells

The core FPGA fabric that implements custom logic consists of 75,000 logic cells, organized into a matrix of configurable logic blocks (CLBs).

- Each CLB contains 8 LUTs and 16 flip-flops

- 256-bit shift registers for memory and delay elements

- Fast carry logic for arithmetic functions

- Low-skew global routing, buffers, and clocks

Built on TSMC’s 16nm FinFET process, the FPGA fabric offers high density and performance per watt. Accelerator blocks like DSP slices connect seamlessly into the interconnect fabric.

Block RAM

For data buffering and storage, the XA7A75T provides 5325 Kb of fast block RAM, organized into 330 dual-port 36 Kb blocks.

Key capabilities:

- Dual or single port configurations

- Optional ECC detection and correction

- Configurable width and depth

- 6000 memory accesses per second

- Cascading for wider memory width

The abundance of block RAM enables on-chip data manipulation without external memories.

DSP Slices

For arithmetic processing, the FPGA includes 240 DSP slices, each providing:

- 25 x 18 bit signed multiply with 48-bit accumulate

- Cascade to 96 bits for high precision

- Optional pipelining and shifting

- Overflow and saturation protection

- Fast DSP carry chain

The many DSP slices enable parallel signal processing tasks for vision, radar, lidar, and machine learning applications.

PCIe Block

The integrated PCIe block provides a x1 Gen2 lane connection, with:

- PCIe 2.1 compliant interface

- 2.5 Gbps line rate

- Auto negotiation speed selection

- AC-coupled differential RX

- Multiply options for refclk input

- MGT and logic interface

This enables high bandwidth local interconnect to processors and other peripherals without consuming FPGA fabric resources.

Ethernet Blocks

Two tri-speed ethernet MAC blocks support 10Mbps, 100Mbps, and 1Gbps operation with:

- 1500 byte jumbo frame support

- RGMII interface to external PHY

- Scatter-gather DMA networking

- Low latency cut-through operation

- Unicast and multicast addressing

Combined with an external PHY, the MAC blocks enable robust automotive ethernet connectivity.

FPGA Clocking

The clocking subsystem allows very flexible control over clock sources, routing, and conditioning:

- Up to 7 clock management tiles (CMTs)

- Mix of PLLs, DLLs, and DCMs

- Frequency synthesis, jitter filtering, and deskew

- Multiple clock input options with muxing

- Global low-skew routing

This provides ultra precise clocks derived from commodity oscillators to sequence critical automotive logic.

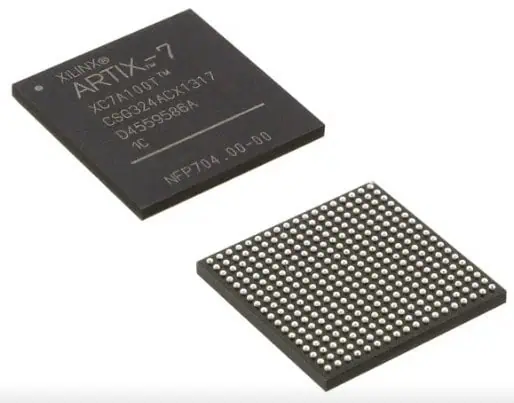

XA7A75T Packaging

The XA7A75T FPGA is packaged in a FCBGA484 package optimized for automotive reliability:

- 15 x 15 mm body, 17 x 17 mm package

- 0.8 mm pitch for escape routing

- 324 user I/O pins

- Corner chamfer indicates pin 1

- Pb-free and RoHS compliant

Rugged -40C to +125C temperature supports under-hood automotive electronics. The 1mm ball pitch enables high connectivity density.

XA Automotive Reliability

The XA FPGAs implement additional automotive-focused reliability measures:

- ERRATA-free ASIC processes

- Full Xilinx standard qualification flow

- Production monitoring and change control

- Enhanced material screening and traceability

- AEC-Q100 Grade 2 certified

- Extended -40C to +125C temperature range

These ensure suitability for safety-critical automotive applications and deliver high long-term reliability.

Development Tools

Xilinx provides a full embedded development toolchain:

- Vivado Design Suite for building hardware

- Vitis tools for creating software

- PetaLinux for Linux OS support

- Model based design with System Generator

- Extensive IP catalog of automotive peripherals

- Reference designs and use cases

These enable rapid development of capable automotive systems leveraging the XA7A75T FPGA.

Conclusion

With its balanced density, ample hardened blocks, power efficiency, and automotive-grade qualification, the Xilinx XA7A75T FPGA provides an optimized platform for advanced driver assistance systems, vehicle connectivity, infotainment, and instrumentation applications. The integrated PCIe, ethernet, memory, and DSP enable necessity in-vehicle functions while minimizing logic resource usage. For automotive engineers looking to add flexible programmable logic, the XA7A75T delivers proven reliability, connectivity, and real-time processing.

Frequently Asked Questions

Q: What are the main advantages of the XA7A75T compared to microcontroller-based designs?

A: The FPGA fabric enables custom parallelism, hardware acceleration, and real-time responsiveness that goes beyond sequential microcontroller execution.

Q: What is the power consumption difference between the XA7A75T vs non-Automotive grade FPGAs?

A: The XA family focuses on minimizing power, with 40% lower static power and up to 30% lower total power versus equivalent non-Automotive devices.

Q: What is the maximum operating speed of the FPGA fabric in the XA7A75T?

A: The typical fMAX is 450MHz. Actual speed depends on the design complexity and routing, with potential to reach over 500MHz in optimized cases.

Q: Does the XA7A75T support functional safety features?

A: Xilinx offers a Safety Package for these FPGAs that provides SEU immunity, fault injection, and other features necessary for ISO 26262 ASIL-B/C compliance.

Q: What is the typical configuration flash storage for the XA7A75T bitstream?

A: A 16MB SPI flash provides ample room for multiple bitstream configurations with redundancy. Smaller serial flashes can work depending on design size.

1. A user configurable analog interface (XADC), incorporating dual 12-bit 1MSPS analog-to-digital converters with on-chip thermal and supply sensors.

2. Single-ended and differential I/O standards with speeds of up to 1.25 Gb/s.

3. 240 DSP48E1 slices with up to 264 GMACs of signal processing.

4. Powerful clock management tiles (CMT), combining phase-locked loop (PLL) and mixed-mode clock manager (MMCM) blocks for high precision and low jitter.

5. Integrated block for PCI Express® (PCIe®), for up to x4 Gen2 Endpoint.

6. Wide variety of configuration options, including support for commodity memories, 256-bit AES encryption with HMAC/SHA-256 authentication, and built-in SEU detection and correction.

7. Low-cost wire-bond packaging, offering easy migration between family members in the same package, all packages available Pb-free.

8. Designed for high performance and lowest power with 28 nm, HKMG, HPL process, 1.0V core voltage process technology.

9. Strong automotive-specific third-party ecosystem with IP, development boards, and design services.

10. Some key features of the CLB architecture include:

11. Real 6-input look-up tables (LUTs) .

12. Memory capability within the LUT .

Register and shift register functionality The LUTs in 7 series FPGAs can be configured as either one 6-input LUT (64-bit ROMs) with one output, or as two 5-input LUTs (32-bit ROMs) with separate outputs but common addresses or logic inputs. Each LUT output can optionally be registered in a flip-flop. Four such LUTs and their eight flip-flops as well as multiplexers and arithmetic carry logic form a slice, and two slices form a configurable logic block (CLB). Four of the eight flip-flops per slice (one per LUT) can optionally be configured as latches. Between 25–50% of all slices can also use their LUTs as distributed 64-bit RAM or as 32-bit shift registers (SRL32) or as two SRL16s. Modern synthesis tools take advantage of these highly efficient logic, arithmetic, and memory features.