In the realm of high-speed printed circuit board (PCB) design, signal integrity is paramount. As clock speeds increase and edge rates become faster, the challenge of managing signal reflections becomes increasingly critical. Signal reflections can lead to distorted waveforms, false triggering, and reduced noise margins, ultimately compromising the reliability and performance of electronic systems. This article delves into the various methods and techniques for suppressing signal reflection in high-speed PCB layouts, providing designers with a comprehensive toolkit to ensure optimal signal integrity.

Understanding Signal Reflection

What Causes Signal Reflection?

Signal reflection occurs when an electrical signal encounters a discontinuity in the transmission line impedance. This discontinuity can be caused by various factors:

- Impedance mismatches

- Vias and layer transitions

- Connectors and component leads

- Trace width or layer changes

- Improper termination

The Impact of Reflections on Signal Integrity

Reflections can have several negative effects on signal integrity:

- Voltage overshoot and undershoot

- Ringing and oscillations

- Increased electromagnetic interference (EMI)

- Reduced timing margins

- False switching and logic errors

Impedance Matching Techniques

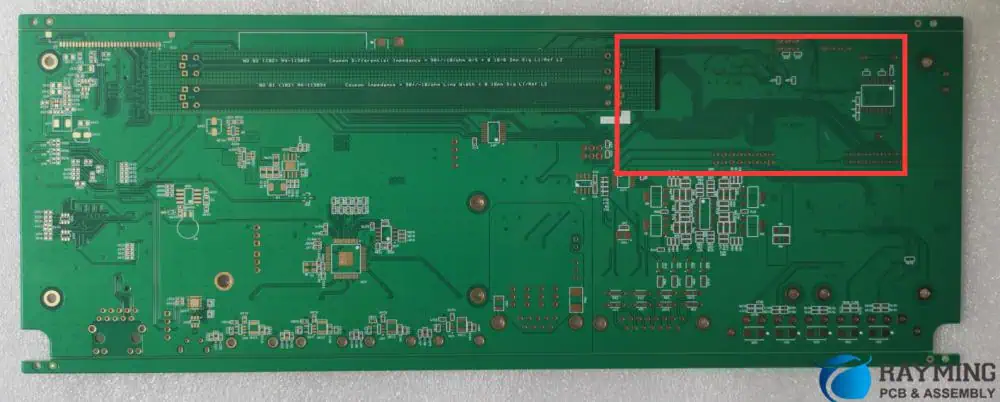

Controlled Impedance Traces

One of the fundamental techniques for reflection suppression is the use of controlled impedance traces.

Common Impedance Values

| Application | Typical Impedance |

| Single-ended | 50Ω or 75Ω |

| Differential | 100Ω or 120Ω |

Impedance Calculation

The impedance of a microstrip or stripline can be calculated using various formulas, considering factors such as trace width, dielectric thickness, and dielectric constant.

Stackup Considerations

Proper stackup design is crucial for maintaining consistent impedance throughout the board.

Stackup Best Practices

- Use adjacent ground planes for microstrip and stripline configurations

- Maintain consistent dielectric thickness

- Consider using high-speed laminates with stable dielectric constants

Termination Strategies

Series Termination

Series termination involves placing a resistor near the signal source to match the trace impedance.

Advantages of Series Termination

- Reduces reflections at the source

- Minimal impact on DC levels

- Low power consumption

Parallel Termination

Parallel termination uses a resistor at the end of the transmission line to match the characteristic impedance.

Types of Parallel Termination

- Simple parallel termination

- Thevenin termination

- AC termination

Active Termination

Active termination uses voltage-controlled current sources or other active components to dynamically match impedance.

Via Design and Optimization

Via Types and Selection

Choosing the appropriate via type is crucial for minimizing reflections at layer transitions.

Common Via Types

| Via Type | Description | Best Use Case |

| Through-hole | Spans all layers | General purpose |

| Blind | Connects outer to inner layer | High-density designs |

| Buried | Connects inner layers | High-layer count boards |

| Microvias | Small diameter, typically laser-drilled | HDI designs |

Via Stub Removal

Via stubs can cause significant reflections and should be minimized or eliminated.

Stub Reduction Techniques

- Back-drilling

- Buried vias

- Stacked microvias

Via Spacing and Placement

Proper via spacing and placement can help maintain signal integrity.

Via Placement Guidelines

- Place vias close to the source for series-terminated lines

- Use multiple vias for power and ground connections

- Maintain consistent via spacing for differential pairs

Trace Routing Techniques

Length Matching

Matching trace lengths is crucial for maintaining timing relationships and reducing reflections in parallel buses.

Length Matching Tolerance

| Signal Type | Typical Tolerance |

| Single-ended | ±5% of total length |

| Differential | ±2.5% of total length |

Serpentine Routing

Serpentine routing is used to add length to shorter traces for length matching purposes.

Serpentine Design Rules

- Maintain minimum bend radius

- Avoid sharp corners (use 45-degree or arc bends)

- Keep serpentines away from sensitive areas

Differential Pair Routing

Proper differential pair routing is essential for maintaining common-mode rejection and reducing reflections.

Differential Routing Guidelines

- Maintain consistent spacing between the pair

- Route differential pairs closely coupled

- Avoid splits in the reference plane beneath the pair

Power Integrity and Its Impact on Reflections

Proper Decoupling

Effective decoupling reduces power supply noise and helps maintain signal integrity.

Decoupling Capacitor Selection

| Frequency Range | Capacitor Type |

| Low (< 10 MHz) | Bulk electrolytic |

| Medium (10 MHz – 100 MHz) | Ceramic MLCC |

| High (> 100 MHz) | Low-ESR ceramic |

Power Plane Design

Well-designed power planes provide low-impedance power distribution and help reduce reflections.

Power Plane Best Practices

- Use solid planes rather than traces for power distribution

- Implement proper plane separation

- Use stitching vias to connect split planes

Advanced Reflection Suppression Techniques

Pre-emphasis and De-emphasis

Pre-emphasis and de-emphasis techniques can be used to compensate for channel losses and reduce reflections.

Pre-emphasis Implementation

- Transmitter-based pre-emphasis

- Receiver-based equalization

- Adaptive equalization techniques

Spread Spectrum Clocking

Spread spectrum clocking can help reduce EMI and mitigate the effects of reflections.

Spread Spectrum Parameters

| Parameter | Typical Range |

| Modulation Rate | 30-33 kHz |

| Modulation Amplitude | 0.5-1% of center frequency |

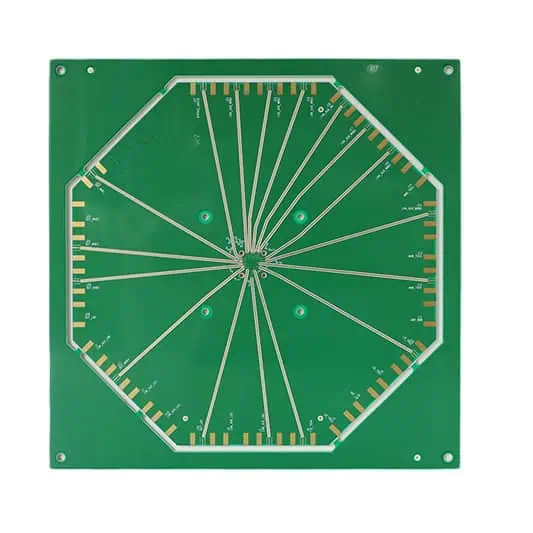

Electromagnetic Band Gap (EBG) Structures

EBG structures can be used to suppress specific frequency bands and reduce reflections.

EBG Applications

- Power plane noise suppression

- Isolation of sensitive circuits

- Reduction of edge-launched surface waves

Signal Integrity Simulation and Analysis

Time Domain Reflectometry (TDR)

TDR analysis is a powerful tool for identifying and locating impedance discontinuities.

TDR Measurement Parameters

- Rise time

- Incident voltage

- Reflection coefficient

S-Parameter Analysis

S-parameters provide a comprehensive characterization of high-speed interconnects.

Key S-Parameters

- S11 (Return Loss)

- S21 (Insertion Loss)

- S31 (Near-end Crosstalk)

- S41 (Far-end Crosstalk)

Eye Diagram Analysis

Eye diagrams offer a visual representation of signal quality and can help identify reflection-related issues.

Eye Diagram Metrics

- Eye height

- Eye width

- Jitter

- Bit error rate (BER)

PCB Material Considerations

Dielectric Material Selection

Choosing the right dielectric material is crucial for maintaining consistent impedance and reducing signal loss.

Common High-Speed PCB Materials

| Material | Dk Range | Df Range | Best Use Case |

| FR-4 | 3.8-4.8 | 0.01-0.02 | General purpose |

| Rogers 4350B | 3.48 | 0.0037 | High-frequency |

| Megtron 6 | 3.4 | 0.002 | Low-loss, high-speed |

Copper Foil Considerations

The type and quality of copper foil can impact signal integrity and reflection suppression.

Copper Foil Types

- Standard ED copper

- Reverse-treated foil (RTF)

- Very low profile (VLP) foil

Manufacturing and Testing Considerations

Controlled Impedance Manufacturing

Working closely with PCB manufacturers to ensure controlled impedance fabrication is crucial.

Manufacturing Specifications

- Dielectric thickness tolerances

- Copper thickness tolerances

- Trace width tolerances

Signal Integrity Testing

Implementing comprehensive signal integrity testing helps verify reflection suppression efforts.

Testing Methods

- Vector Network Analyzer (VNA) measurements

- TDR/TDT testing

- Bit Error Rate Testing (BERT)

Conclusion

Suppressing signal reflections in high-speed PCB layouts requires a multifaceted approach, combining proper design techniques, material selection, and advanced analysis methods. By implementing the strategies outlined in this article, PCB designers can significantly improve signal integrity, leading to more reliable and higher-performing electronic systems.

Frequently Asked Questions

Q1: How do I determine if signal reflection is a significant issue in my PCB design?

A1: Several indicators can suggest that signal reflection is a significant issue:

- Ringing or oscillations on signal waveforms

- Unexplained EMI problems

- Intermittent system failures or data errors

- Poor eye diagram measurements (reduced eye height or width)

- Failed signal integrity tests (e.g., TDR measurements showing large discontinuities)

To determine if reflection is the root cause, you can:

- Perform time-domain reflectometry (TDR) analysis

- Conduct S-parameter measurements

- Use signal integrity simulation tools to model and analyze the design

- Examine eye diagrams for signal quality issues

If these analyses reveal significant impedance discontinuities or waveform distortions, signal reflection is likely a concern that needs to be addressed.

Q2: What are the trade-offs between different termination methods?

A2: The main termination methods (series, parallel, and active) each have their own trade-offs:

- Series Termination:

- Pros: Low power consumption, minimal impact on DC levels

- Cons: Signal delay, not suitable for multi-drop buses

- Parallel Termination:

- Pros: Effective for multi-drop buses, maintains signal integrity at receiver

- Cons: Higher power consumption, can impact DC levels

- Active Termination:

- Pros: Adaptable to changing conditions, can handle complex impedance matching

- Cons: Higher cost, increased complexity, potential for additional noise

The choice depends on factors such as:

- Signal characteristics (frequency, rise time)

- Board topology (point-to-point vs. multi-drop)

- Power budget

- Cost constraints

- Available board space

Consider these factors carefully when selecting the most appropriate termination method for your specific design requirements.

Q3: How can I effectively manage reflections in high-speed differential pairs?

A3: Managing reflections in high-speed differential pairs involves several key strategies:

- Maintain consistent differential impedance (typically 100Ω or 120Ω) throughout the entire path.

- Use symmetrical routing to ensure equal length and impedance for both signals in the pair.

- Keep the pair tightly coupled to maintain common-mode rejection.

- Avoid splits in the reference plane beneath the differential pair.

- Use appropriate differential termination techniques, such as:

- Differential series termination near the source

- Differential parallel termination at the receiver

- Minimize via transitions and ensure symmetry when transitions are necessary.

- Use matched-length vias for layer changes.

- Implement careful length matching between pairs in multi-pair buses.

- Consider using high-quality, low-loss PCB materials for critical differential pairs.

- Perform differential TDR and eye diagram analysis to verify pair performance.

By applying these techniques, you can significantly reduce reflections and maintain signal integrity in high-speed differential pairs.

Q4: What role does PCB stackup design play in reflection suppression?

A4: PCB stackup design plays a crucial role in reflection suppression:

- Impedance Control: Proper stackup ensures consistent impedance for signal layers, minimizing reflections due to impedance variations.

- Return Path: A well-designed stackup provides continuous return paths for high-speed signals, reducing discontinuities.

- Crosstalk Reduction: Strategic layer ordering and spacing can minimize crosstalk, which can contribute to reflections.

- Power Integrity: Incorporating dedicated power and ground planes helps maintain a stable power distribution network, reducing noise-induced reflections.

- Via Performance: The stackup influences via stub length and overall via performance, affecting signal transitions between layers.

- Dielectric Thickness: Consistent dielectric thickness between layers helps maintain uniform impedance.

- Material Selection: The stackup determines which materials are used for each layer, impacting overall signal loss and impedance stability.

- EMI Control: Proper shielding layers in the stackup can reduce EMI, which can indirectly contribute to signal integrity issues.

A carefully designed stackup is foundational to effective reflection suppression in high-speed PCB layouts.

Q5: How do I balance reflection suppression techniques with other design constraints like cost and manufacturability?

A5: Balancing reflection suppression with cost and manufacturability involves several considerations:

- Material Selection:

- Use standard FR-4 for less critical signals

- Reserve high-performance (and costlier) materials for critical high-speed sections

- Layer Count:

- Optimize layer count to balance signal integrity needs with cost

- Consider using hybrid stackups with selective use of high-performance materials

- Via Strategy:

- Use through-hole vias where possible for lower cost

- Implement back-drilling or blind/buried vias only for critical signals

- Termination:

- Use series termination where applicable to reduce component count

- Implement parallel termination judiciously, considering power consumption

- Trace Geometry:

- Design traces within standard manufacturing tolerances

- Use controlled impedance only where necessary

- Component Selection:

- Design for Testability:

- Incorporate test points for critical signals to enable easier manufacturing verification

- Simulation and Analysis:

- Utilize simulation tools early in the design process to optimize designs before committing to manufacturing

- Manufacturing Partnerships:

- Work closely with PCB manufacturers to understand their capabilities and limitations

- Design Rules:

- Develop and adhere to design rules that balance performance requirements with manufacturability

By carefully considering these factors, you can achieve effective reflection suppression while maintaining reasonable cost and manufacturability in your high-speed PCB designs.