The transformation of artificial intelligence from laboratory curiosity to consumer necessity has catalyzed a remarkable evolution in wearable technology. Among the most compelling manifestations of this convergence are AI-powered smart glasses, devices that have transcended their science fiction origins to become sophisticated platforms for human-computer interaction. These innovative wearables represent a paradigm shift in how we access and process information, offering unprecedented convenience through seamless integration of advanced computing capabilities into an unobtrusive form factor.

Today’s AI smart glasses ecosystem encompasses a diverse array of applications that extend far beyond simple augmented reality overlays. Users can leverage these devices for teleprompting during presentations, capturing high-quality photographs with intelligent scene recognition, performing real-time object identification and translation, accessing turn-by-turn navigation without visual distraction, monitoring health metrics continuously, and even conducting contactless payments. This comprehensive functionality positioning makes AI glasses an ideal platform for the next generation of human-machine interaction applications, eliminating the need for users to constantly retrieve and manipulate their smartphones.

The Fundamental Power Challenge

Despite their impressive capabilities, AI smart glasses face a critical engineering challenge that threatens to limit their widespread adoption: power consumption management. The fundamental constraint stems from the inherent conflict between performance requirements and physical limitations. To maintain user comfort and aesthetic appeal, smart glasses must remain lightweight, typically weighing less than 30 grams. This weight restriction severely limits battery capacity, with most devices incorporating batteries ranging from just 200 to 300mAh – a fraction of what modern smartphones provide.

The power challenge becomes even more complex when considering the computational demands of AI applications. High-performance application processors required for advanced AI functions typically utilize cutting-edge semiconductor process nodes of 6nm and below. While these advanced manufacturing processes deliver exceptional dynamic performance and computational density, they introduce a significant drawback: exponentially increasing leakage current as transistor dimensions shrink.

This leakage current represents power consumption that occurs even when the processor is not actively performing computations, creating a constant drain on the limited battery capacity. The mathematical relationship between process node advancement and leakage current creates a fundamental trade-off where the very technology that enables sophisticated AI capabilities simultaneously undermines the battery life that makes the device practical for everyday use. This conflict between high-performance processing requirements and stringent power budgets has become the defining challenge in AI glasses development.

Architectural Approaches to Power Optimization

The industry has responded to these power challenges by developing two primary architectural approaches, each representing different trade-offs between functionality and efficiency.

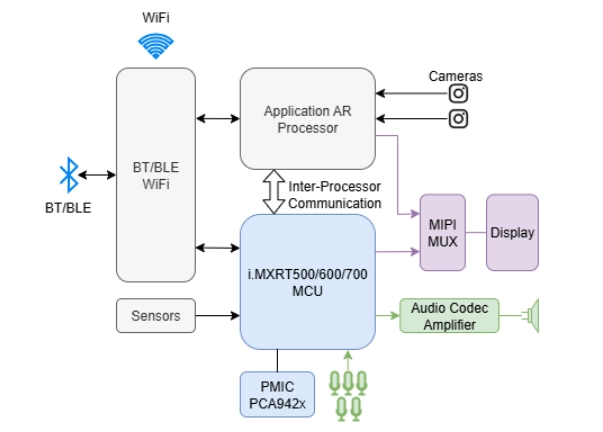

The Application Processor Plus Coprocessor Architecture

The first approach employs a dual-processor strategy that separates high-performance computing tasks from always-on functions. This “Application Processor + Coprocessor” architecture enables manufacturers to deliver feature-rich devices without completely sacrificing battery life.

The application processor in this configuration serves as the powerhouse, built using advanced process technology to maximize computational performance. This processor handles demanding tasks including high-resolution image and video processing, complex neural network computations through dedicated Neural Processing Units (NPUs), and high-bandwidth wireless connectivity via Wi-Fi and Bluetooth modules. When active, this processor delivers the computational horsepower necessary for sophisticated AI applications such as real-time object recognition, natural language processing, and augmented reality rendering.

Complementing this high-performance processor is a carefully designed coprocessor that prioritizes efficiency over raw computational power. This secondary processor typically employs more mature semiconductor manufacturing processes that offer better power characteristics for always-on operations. The coprocessor integrates optimized transistor designs, combining long-channel and short-channel devices to achieve superior power efficiency during low-frequency operations and minimize static power consumption.

The coprocessor assumes responsibility for continuous background functions including voice wake-up detection, audio processing for calls and music playback, and basic user interface rendering. Its integrated GPU enables vector graphics processing and text rendering for essential display functions, while a dedicated AI acceleration unit enhances voice recognition accuracy and provides real-time noise reduction capabilities.

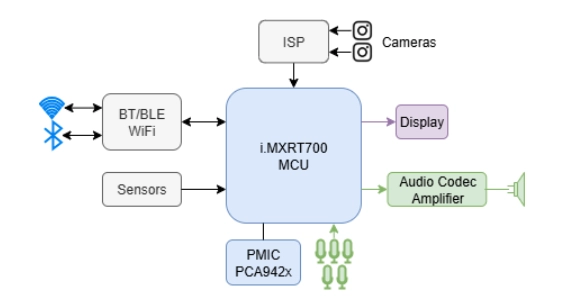

The Low-Power Processor Main Control Architecture

The alternative architectural approach prioritizes maximum battery life and user comfort through a single, highly optimized low-power processor serving as the main system controller. This strategy recognizes that user experience in wearable devices is fundamentally constrained by weight and battery life, leading to a design philosophy that emphasizes efficiency over maximum performance.

This architecture reduces system complexity by eliminating the need for multiple high-power processors and their associated support circuitry. The reduction in component count and power requirements enables manufacturers to utilize smaller batteries and eliminate bulky power management components, keeping total device weight under the critical 30-gram threshold that research has identified as the maximum acceptable weight for extended wear comfort.

While this approach may limit the complexity of AI applications that can be supported, it enables devices that users can comfortably wear throughout an entire day without frequent charging interruptions.

NXP’s i.MX RT Series: Breaking Through Traditional Limitations

NXP Semiconductors has developed a family of processors specifically designed to address the unique challenges of AI-powered wearable devices. The i.MX RT500, RT600, and RT700 processors represent progressive generations of low-power computing solutions that have been widely adopted in innovative AI glasses worldwide.

i.MX RT500: Foundation for Audio-Centric Applications

The i.MX RT500, featuring the Fusion F1 DSP architecture, establishes the foundation for audio-centric smart glasses applications. This processor excels at voice wake-up functionality, high-quality music playback, and hands-free calling capabilities. Its integrated GPU supports VGA-resolution displays, enabling basic visual interfaces while maintaining exceptional power efficiency.

i.MX RT600: Advanced Audio Processing Capabilities

Building upon the RT500 foundation, the i.MX RT600 incorporates a powerful 600MHz HiFi4 DSP that significantly enhances audio processing capabilities. This processor excels at computationally intensive audio algorithms including multi-microphone noise reduction, advanced beamforming for directional audio capture, and sophisticated wake-word detection that can operate reliably in challenging acoustic environments.

i.MX RT700: Next-Generation AI Integration

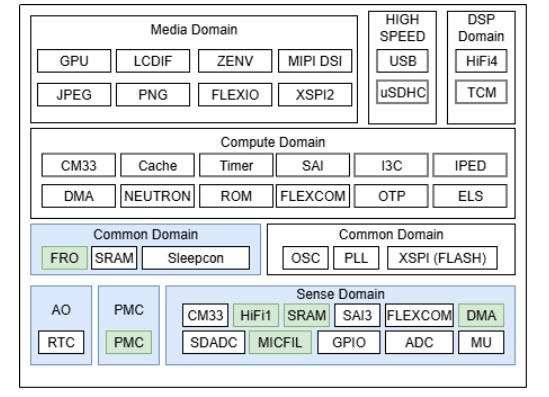

The latest i.MX RT700 represents a significant evolutionary leap, incorporating a dual-DSP architecture that combines HiFi4 and HiFi1 processors to support complex, multi-layered algorithms simultaneously. The processor’s advanced 2.5D GPU and MIPI DSI interface enable smooth 720p video rendering at 60 frames per second, while the integrated Neutron NPU provides dedicated AI acceleration accessible through NXP’s comprehensive eIQ machine learning toolkit.

Advanced Power Management Technologies

The i.MX RT series processors integrate multiple sophisticated power-saving technologies that work synergistically to extend battery life. These include implementation of the I3C bus protocol for more efficient inter-chip communication, dynamic voltage scaling that adjusts operating voltages in real-time based on computational demands, and specialized low-leakage SRAM designs that minimize static power consumption.

Additional power optimization features include Process, Voltage, and Temperature (PVT) sensors that enable intelligent performance scaling, ultra-low-power clock sources that reduce timing-related power consumption, and sophisticated power domain switching that allows different processor subsystems to be independently managed.

i.MX RT700 Efficiency Breakthrough

The i.MX RT700 demonstrates remarkable efficiency improvements over its predecessors, achieving 45% lower dynamic power consumption compared to the i.MX RT600 while delivering 80% lower static power consumption – representing just 20% of the RT600’s standby power requirements.

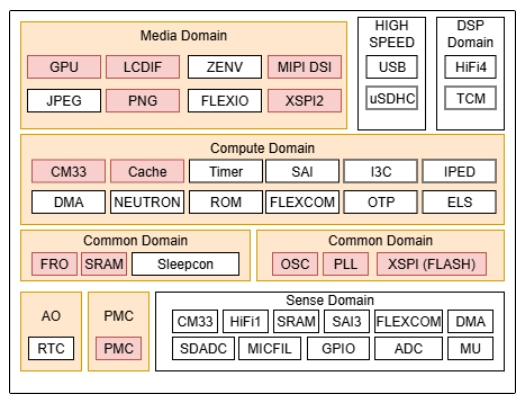

This efficiency breakthrough results from fine-grained power partitioning that divides the system-on-chip into five distinct domains: the Main Compute Domain for primary processing tasks, the Sense Compute Domain for sensor data processing, the Media Domain for audio and video functions, the Power Control Domain for system management, and the Always-On Domain for continuous background operations.

Each domain can be independently powered on or off based on current system requirements, with dynamic voltage scaling applied individually to optimize performance-per-watt ratios across different operating scenarios.

Dynamic Mode Switching for Optimal Efficiency

The i.MX RT700’s architecture enables sophisticated power management through dynamic role switching based on current application requirements. This capability allows the processor to seamlessly transition between high-performance multimedia processing and ultra-low-power sensor monitoring modes.

Ultra-Low-Power Sensor Hub Mode

During periods when the glasses are waiting for voice activation, the system enters Sensor Hub mode, where only essential components remain active. The HiFi1 DSP, DMA controllers, digital microphone filter (MICFIL), and minimal SRAM continue operating to maintain voice wake-up functionality. All other system components power down completely, reducing total system power consumption to an remarkable 1.91mW.

This exceptional efficiency results from utilizing low-power FRO clock sources, hardware-based Voice Activity Detection (VAD) that minimizes DSP wake-up events, and intelligent DMA wake-up mechanisms that activate processing resources only when audio activity is detected.

High-Performance Multimedia Mode

When display-intensive applications are active, the system transitions to high-performance mode, activating the GPU, LCD controller, MIPI DSI interface, and external frame buffer memory. Even in this demanding operational mode, power-saving features including MIPI Ultra-Low Power State (ULPS) and dynamic voltage scaling remain enabled to minimize unnecessary power consumption.

System-Level Power Management Integration

Effective power management in AI glasses extends beyond the main processor to encompass dedicated Power Management Integrated Circuits (PMICs) that optimize system-wide efficiency. NXP offers specialized PMICs designed specifically for their i.MX RT processor family.

The PCA9420, designed for i.MX RT500 and RT600 systems, provides 315mA charging capability with two Buck converters and two LDO regulators for comprehensive power distribution. For the more advanced i.MX RT700, the PCA9422 PMIC offers enhanced 640mA charging with three Buck converters, four LDO regulators, one Buck-Boost converter, and integrated FLEXGAUGE software fuel gauge functionality.

These PMICs enable sophisticated Dynamic Voltage Scaling (DVS) capabilities, automatically adjusting supply voltages based on current performance requirements and power modes to maximize battery utilization efficiency.

Conclusion and Future Outlook

The convergence of artificial intelligence and smart hardware continues accelerating, with AI-powered smart glasses representing one of the most promising frontiers for human-computer interaction innovation. Success in this rapidly evolving market fundamentally depends on selecting processors that can deliver the sophisticated AI capabilities users demand while maintaining the exceptional power efficiency that practical wearable devices require.

NXP’s i.MX RT processor series, backed by decades of embedded systems expertise and continuous innovation in low-power design, provides manufacturers with a proven foundation for developing cutting-edge AI glasses that can meet both performance expectations and real-world usability requirements. As the technology continues maturing, these power-efficient processing solutions will prove instrumental in transforming AI glasses from niche products into ubiquitous tools that seamlessly integrate into our daily lives.

Related posts:

- Analog Circuits on PCBs: Design Principles, Challenges, and Best Practices

- What You Should Know About Fares PCB Assembly – PCB Design for Smart Card, RFID, and Other Circuits

- Flex Circuit Technologies – Design Incredible Smart Devices On The Go

- What is the Difference Between ARM and FPGA Processors?