Introduction

The Xilinx CoolRunner-II XCR3064XL-7PC44I is a low-power CPLD (complex programmable logic device) that provides medium density, performance, and an abundance of I/O in a compact form factor. The XCR3064XL balances logic capacity with low static and dynamic power consumption, making it an excellent fit for a wide variety of embedded applications.

In this article, we will take a technical deep dive into the capabilities, architecture, and key parameters of the XCR3064XL-7PC44I to understand where it excels and how to leverage its unique characteristics. We’ll explore the datasheet specifications and discuss example usage scenarios that can benefit from this CoolRunner-II device.

XCR3064XL Overview

Here are some of the high-level features of the Xilinx XCR3064XL-7PC44I CPLD:

- 64 macrocells providing 15,000 usable gates

- Maximum clock speed of 350 MHz

- 144 total user I/O pins

- 7ns pin-to-pin delays

- 1.2V VCCINT core supply voltage

- 0.9W typical power consumption

- 7 x 7 mm 144-pin TQFP package

- Operating temperature from 0°C to 85°C

This provides a robust amount of logic capacity with fast performance and abundant I/Os in an efficient power envelope.

CPLD Architecture

The XCR3064XL architecture consists of:

- Four sectors each containing macrocell logic blocks

- Macrocells implement logic using product term arrays

- Local interconnect provides intra-sector routing

- Global interconnect enables cross-sector connectivity

- Input/output blocks for pin routing and logic interfacing

By combining continuous interconnect with product term-based macrocells, an optimal balance of flexibility and routability is achieved.

Logic Capacity

With 64 macrocells providing 15,000 usable gates, the XCR3064XL supports reasonably complex logic designs:

- Each macrocell contains a 32-product term lookup table (LUT) for logic implementation

- Wide multiplexers and arithmetic carry logic expand capabilities

- LUTs can also be split into two 16-product term functions

- 15 inputs per macrocell simplify wide input logic

- D-type flip-flop for registered outputs

Typical applications fit comfortably within the available logic space.

Performance

A peak internal clock speed of 350 MHz allows high speed operation:

- Input to output delays as fast as 3.5ns

- 7ns pin-to-pin delays available

- Low clock-to-output delays

- High fan-in capabilities

- Supports source synchronous designs

The XCR3064XL provides responsive performance for time-critical embedded systems.

Power Consumption

At just 0.9W static power and 200mA peak current draw, the XCR3064XL operates efficiently:

- 1.2V VCCINT supply voltage

- 3.3V VCCIO for I/O interfaces

- Low static current in mA range

- Typical 200mW standby power

- Suspend mode drops power to just 45mW

Power saving modes make the XCR3064XL ideal for portable and battery powered electronics.

I/O Capabilities

With 144 total user I/O pins, the CPLD supports a wide range of interfacing needs:

- Flexible I/O banks withvoltage from 1.2V to 3.3V

- Single-ended or differential I/O standards

- Drive strength from 4mA to 24mA

- PCI compliant clamp diodes

- Programmable pull-up resistors

- Slew rate control

Ample I/O pins reduce or eliminate external logic when interfacing with processors, buses, and peripherals.

Configuration and Security

The XCR3064XL loads configuration bitstreams from:

- Serial peripheral interface (SPI) flash

- Direct JTAG programming

- Auto reconfiguration on power up

- AES encryption secures designs

Non-volatile storage allows instant start up after loss of power. Encryption safeguards intellectual property.

Development Tools

Xilinx provides the ISE design suite for synthesizing and optimizing CPLD logic:

- VHDL and Verilog support

- XST synthesis tool integrates into ISE flows

- Timing analysis identifies critical paths

- Validate designs with ModelSim simulation

- Xilinx programming hardware loads completed bitstreams

A full embedded development toolchain enables CPLD-based designs with the XCR3064XL.

Conclusion

With its balanced density, ample performance, low power consumption, and abundance of I/O, the Xilinx XCR3064XL-7PC44I CPLD excels at a wide array of embedded system applications. The integrated development environment makes designing with the XCR3064XL accessible for new and experienced users alike. For embeddeed systems where a full FPGA may be overkill but a small CPLD lacks sufficient capacity, the XCR3064XL hits the sweet spot.

Frequently Asked Questions

Q: What are some typical applications suitable for the XCR3064XL CPLD?

A: Example uses including motor control, IoT edge nodes, industrial automation, algorithm accelerators, instrumentation, and interface glue logic.

Q: What density CPLD should be selected if the XCR3064XL does not have sufficient capacity?

A: The larger XC95108 and XC95144/216 CPLDs provide more macrocells and I/O for more complex designs.

Q: How does the XCR3064XL compare to competing CPLDs?

A: It competes with mid-density CPLDs from Lattice, Microsemi, and other vendors, but with lower power and cost.

Q: Does the XCR3064XL support in-system programming and reconfiguration?

A: Yes, via the JTAG interface the CPLD can be reprogrammed unlimited times on the PCB.

Q: What embedded processors work well with the XCR3064XL CPLD?

A: Simple 8-bit CPUs like Microchip PIC16/18, Atmel AVR, and TI MSP430 interface easily. 32-bit ARM cores can also leverage the CPLD.

XCR3064XL-7PC44I Description

The CoolRunner™ XPLA3 XCR3064XL device is a 3.3V, 64-macrocell CPLD targeted at power sensitive designs that require leading edge programmable logic solutions. A total of four function blocks provide 1,500 usable gates. Pin-to-pin propagation delays are as fast as 5.5 ns with a maximum system frequency of 192 MHz.

| Manufacturer | Xilinx Inc. |

| Category | Integrated Circuits (ICs) – Embedded – CPLDs (Complex Programmable Logic Devices) |

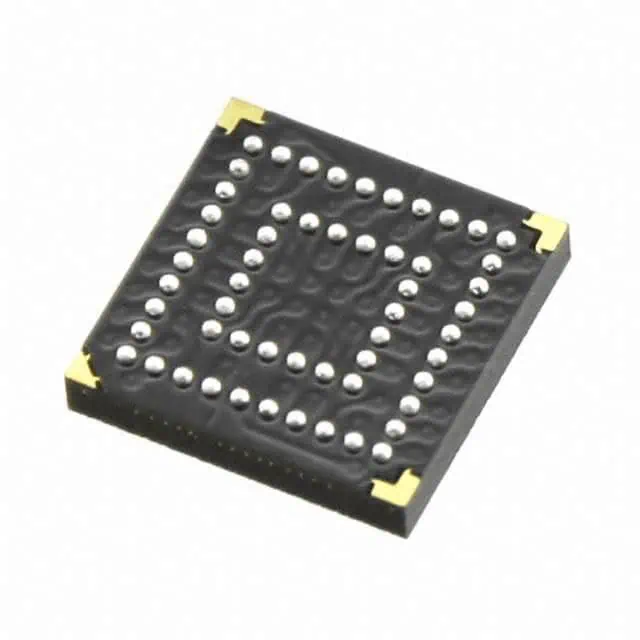

| Package | 44-LCC (J-Lead) |

| Series | CoolRunner XPLA3 |

| Programmable Type | In System Programmable (min 1K program/erase cycles) |

| Delay Time tpd(1) Max | 7.0ns |

| Voltage Supply – Internal | 2.7 V ~ 3.6 V |

| Number of Logic Elements/Blocks | 4 |

| Number of Macrocells | 64 |

| Number of Gates | 1500 |

| Number of I/O | 36 |

| Operating Temperature | -40°C ~ 85°C (TA) |

| Mounting Type | Surface Mount |

| Package / Case | 44-LCC (J-Lead) |

| Supplier Device Package | 44-PLCC (16.59×16.59) |

You also could found the family series as below:

| XCR3064XL-10PC44C |

| XCR3064XL-7PC44C |

| XCR3064XL-7PC44I |