DS-7409HF halogen-free laminate from Doosan: RoHS compliant, 150°C Tg, CTI ≥600V. Full specs, competitor comparison & PCB engineering guide.

If you’ve been specifying PCB laminates for any product that needs to ship into Europe, Japan, or virtually any regulated market, the phrase “halogen-free” has probably been sitting on your BOM checklist for years now. The DS-7409HF halogen-free laminate from Doosan Electro-Materials is one of those materials that keeps showing up in multilayer PCB stackups — and for good reason. In this guide, I’ll break down exactly what makes this material tick, how it maps to RoHS and IEC halogen-free standards, and where it genuinely fits (and where it doesn’t) in your next design.

What Is the DS-7409HF Halogen-Free Laminate?

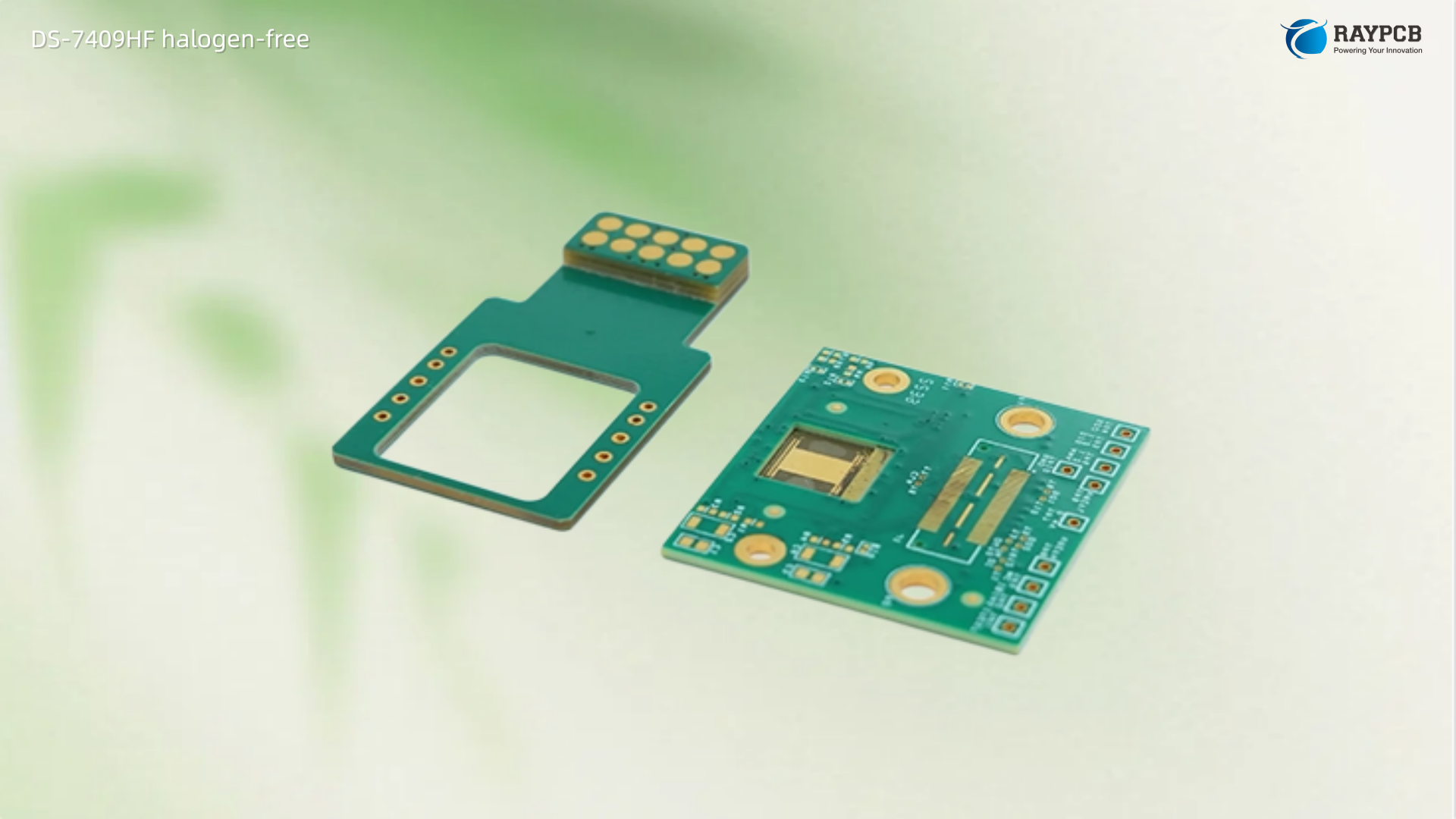

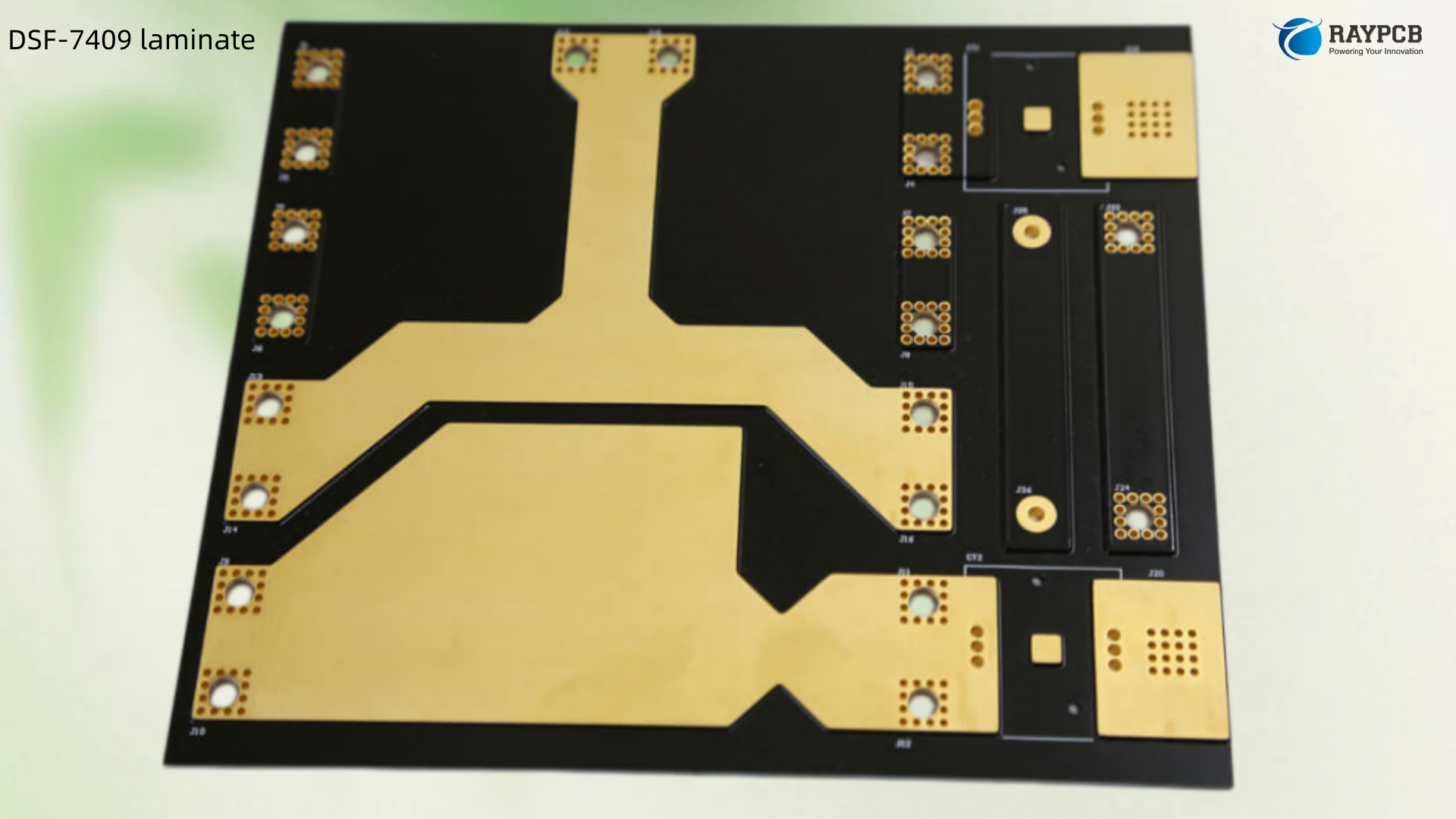

The DS-7409HF is a high-Tg, halogen-free, FR-4-class copper-clad laminate (CCL) produced by Doosan PCB Electro-Materials, a South Korean specialty chemicals and electronic materials company. It belongs to Doosan’s DS-7400 series, which is engineered specifically to meet modern environmental and thermal reliability requirements.

Unlike standard FR-4, which uses brominated flame retardants (BFRs) to meet UL 94 V-0, the DS-7409HF uses phosphorus-based and nitrogen-based flame retardant chemistry — no chlorine, no bromine above trace levels. This makes it genuinely halogen-free per IEC 61249-2-21, not just “low-halogen.”

For PCB engineers, this distinction matters. Many materials labeled “halogen-free” are simply low-halogen. IEC 61249-2-21 sets specific thresholds:

| Halogen | IEC 61249-2-21 Limit |

| Chlorine (Cl) | ≤ 900 ppm |

| Bromine (Br) | ≤ 900 ppm |

| Total halogens | ≤ 1500 ppm |

DS-7409HF meets all three thresholds comfortably.

DS-7409HF Key Technical Specifications

Here’s a quick-reference table for the most critical parameters engineers pull when qualifying a laminate:

| Property | Test Method | Typical Value |

| Glass Transition Temperature (Tg) | DSC (IPC-TM-650 2.4.25) | 150°C |

| Decomposition Temperature (Td) | TGA (5% weight loss) | ≥ 340°C |

| T-288 (time-to-delamination) | IPC-TM-650 2.4.24.1 | > 10 min |

| CTE (Z-axis, 50–260°C) | TMA | ≤ 3.5% |

| CTI (Comparative Tracking Index) | IEC 60112 | ≥ 600 V (Group I) |

| Dielectric Constant (Dk) @ 1 GHz | IPC-TM-650 2.5.5.9 | ~4.5 |

| Dissipation Factor (Df) @ 1 GHz | IPC-TM-650 2.5.5.9 | ~0.015 |

| Flexural Strength (lengthwise) | IPC-TM-650 2.4.4 | ≥ 415 MPa |

| Water Absorption | IPC-TM-650 2.6.2 | ≤ 0.15% |

| Flammability | UL 94 | V-0 |

| RoHS Compliance | EU Directive 2011/65/EU | Yes |

The T-288 value is probably the most practically useful number on that table. It tells you how long the laminate can survive at 288°C (typical lead-free solder pot temperature) before delamination begins. Anything above 10 minutes is solid for lead-free assembly. DS-7409HF clears that comfortably.

RoHS Compliance: What It Actually Means for DS-7409HF

RoHS (Restriction of Hazardous Substances, EU Directive 2011/65/EU, updated by 2015/863/EU) restricts ten substances in electrical and electronic equipment. For laminate materials, the most relevant restrictions are:

- Lead (Pb): ≤ 0.1% by weight in homogeneous materials

- Cadmium (Cd): ≤ 0.01%

- Hexavalent chromium (Cr VI): ≤ 0.1%

- Polybrominated biphenyls (PBB): ≤ 0.1%

- Polybrominated diphenyl ethers (PBDE): ≤ 0.1%

DS-7409HF satisfies all ten RoHS restricted substance limits. Since it contains no brominated flame retardants at all, PBB and PBDE concerns are eliminated at the chemistry level — not just managed to stay under threshold.

This is an important point for product compliance documentation. When your customer asks for a full material declaration (FMD) or an IPC-1752A Class D declaration, having a material with zero brominated content is much cleaner to document than one that’s simply “under limit.”

REACH and SCIP Considerations

Beyond RoHS, the EU REACH regulation (SVHC substances of very high concern) and the SCIP database requirements increasingly affect PCB laminate sourcing. Doosan provides REACH compliance documentation for DS-7409HF, confirming no SVHC substances above 0.1% threshold.

Why PCB Engineers Choose DS-7409HF Halogen-Free Over Standard FR-4

Thermal Performance at Lead-Free Assembly Temperatures

The industry shift to lead-free soldering (SAC305 alloy, peak reflow at ~260°C) put a lot of pressure on laminates that were designed for eutectic tin-lead (peak ~183°C). Standard FR-4 with Tg of 130°C struggles. DS-7409HF’s 150°C Tg and ≥340°C Td give you meaningful margin above lead-free reflow peaks, especially important for thick multilayer boards with many reflow cycles.

Moisture Absorption and Long-Term Reliability

Water absorption directly affects signal integrity at high frequencies and dimensional stability. At ≤ 0.15%, DS-7409HF is notably better than many standard halogen-free alternatives which can creep toward 0.2–0.3%. For outdoor telecom enclosures, industrial control boards, or automotive ADAS modules, this matters.

CTI ≥ 600V — Practical Impact

CTI (Comparative Tracking Index) of Group I (≥ 600V) isn’t just a spec box to check — it directly affects your PCB creepage and clearance calculations under IEC 60664-1. A higher CTI material allows smaller creepage distances for a given voltage level, which can meaningfully reduce board area on high-voltage industrial or EV charging designs.

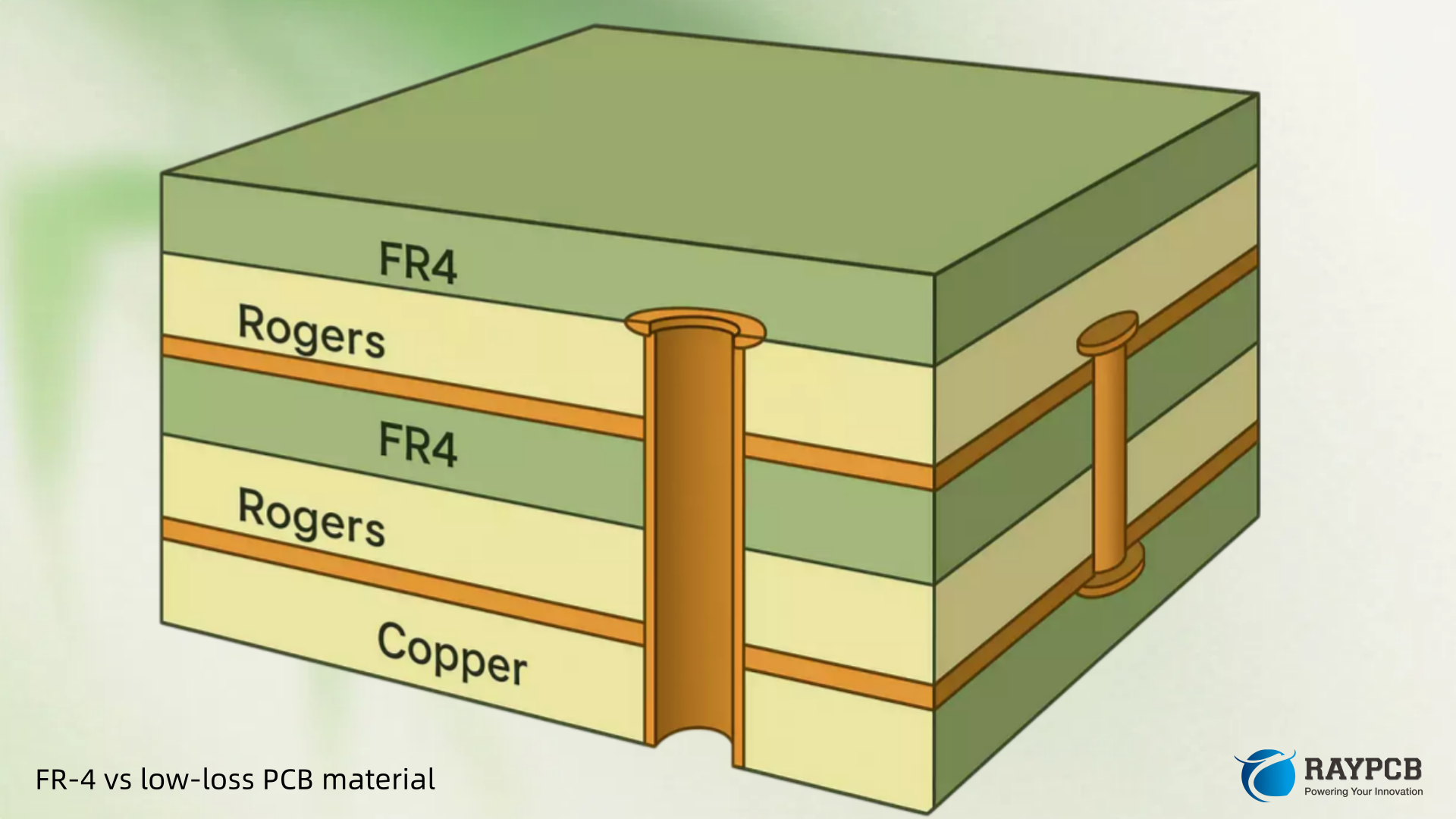

DS-7409HF vs. Competing Halogen-Free Laminates

How does it stack up against other commonly specified halogen-free materials?

| Material | Manufacturer | Tg (°C) | Td (°C) | CTI | Dk @ 1GHz | Notable Use Case |

| DS-7409HF | Doosan | 150 | ≥ 340 | ≥ 600 V | ~4.5 | Industrial, Automotive |

| IT-158 | Iteq | 150 | 360 | ≥ 600 V | ~4.6 | Telecom, Server |

| S1000-2M | Sytech | 170 | 340 | ≥ 600 V | ~4.8 | High-layer Multilayer |

| TU-768 | TUC | 175 | 360 | ≥ 600 V | ~4.6 | High-Reliability Industrial |

| Megtron 6 | Panasonic | 185 | 400 | ≥ 600 V | ~3.7 | High-Speed Digital, RF |

DS-7409HF sits in the sweet spot for cost-performance balance — better thermal performance than entry-level halogen-free FR-4 derivatives, without the price premium of high-speed laminates like Megtron 6 (which you probably don’t need unless your signals are running above 10 Gbps).

Typical Applications for DS-7409HF Halogen-Free Laminate

Based on its property profile, DS-7409HF is well-suited for:

- Industrial control boards — motor drives, PLCs, power converters

- Automotive electronics — body control modules (BCM), ADAS sensor interfaces (not cutting-edge radar, but tier-2 functional boards)

- Telecommunications infrastructure — access network equipment, switches, routers

- Medical equipment PCBs — where halogen-free is increasingly a procurement requirement

- LED lighting drivers — high-temperature ambient environments

- Power supply PCBs — where CTI Group I provides design flexibility

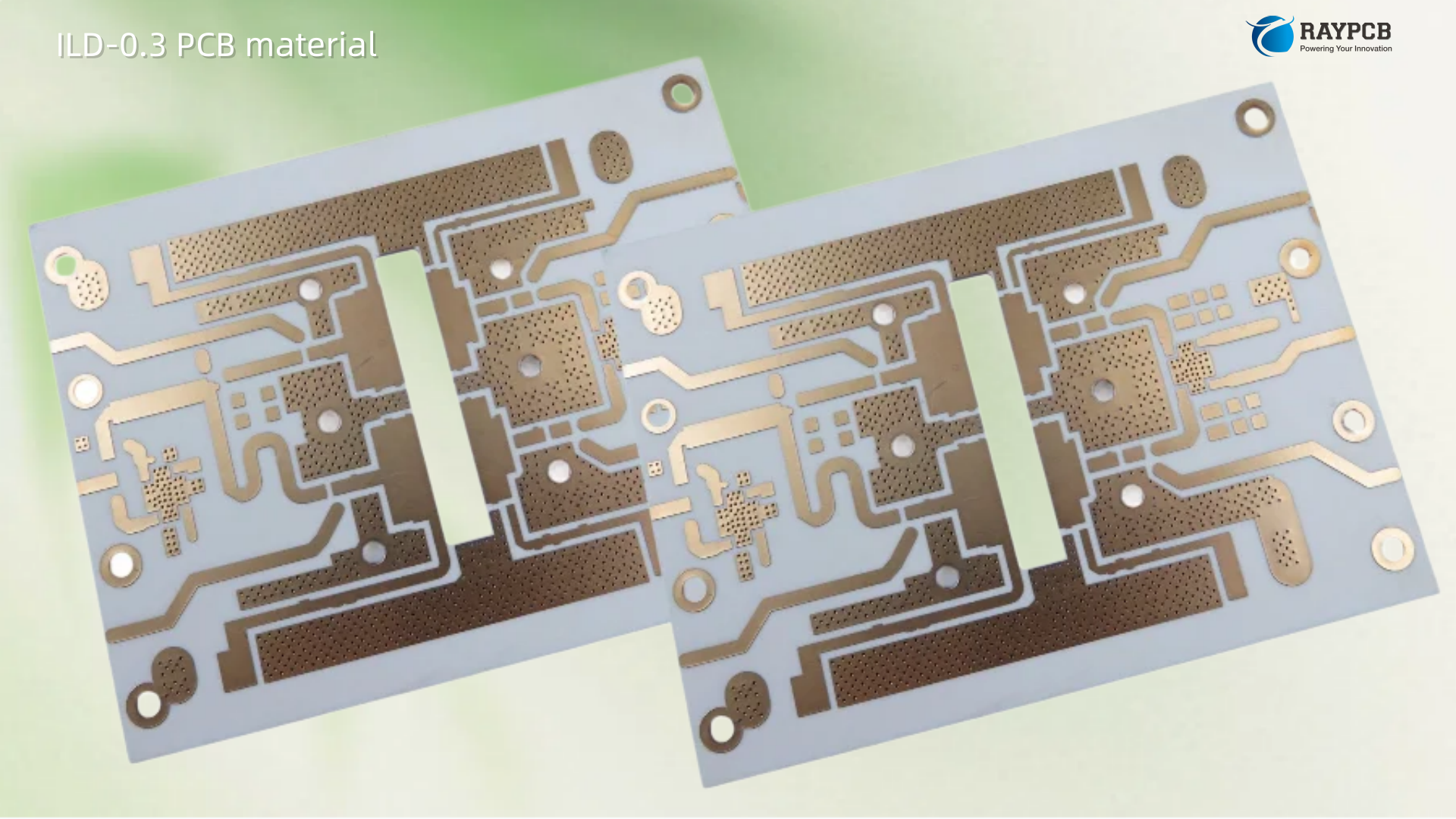

It’s generally not the right call for high-frequency RF boards above ~6 GHz (Dk/Df isn’t optimized for that), or extreme thermal cycling automotive applications (dedicated automotive-grade materials are better there).

Processing Guidelines for DS-7409HF

A few practical notes for your fab and assembly teams:

Drilling: Halogen-free laminates tend to be slightly more brittle than standard FR-4 due to the different resin chemistry. Use fresh drill bits, and reduce feed rate by ~10% compared to your standard FR-4 baseline to avoid drill smear.

Desmear: The higher cross-link density in halogen-free resins means desmear needs to be slightly more aggressive. Confirm with your fab house that their permanganate desmear cycle is calibrated for HF materials — not all fab lines default to this.

Storage: Keep panels in sealed moisture barrier bags with desiccant at 20–30°C, below 60% RH. Pre-bake at 120°C for 2–4 hours before lamination if panels have been exposed beyond manufacturer’s shelf-life window.

Lead-Free Reflow: Compatible with SAC305. Typical peak reflow at 245–260°C. The T-288 margin of >10 minutes covers multiple reflow cycles without issue.

Useful Resources for DS-7409HF Halogen-Free Laminate

| Resource | Description | Link |

| IPC-4101 | Base Materials for Rigid and Multilayer PCBs (laminate spec standard) | ipc.org |

| IEC 61249-2-21 | Halogen-free definition and test methodology | iec.ch |

| EU RoHS Directive 2011/65/EU | Full restricted substance list | ec.europa.eu |

| IPC-TM-650 | Test Methods Manual (laminate property testing) | ipc.org/TM-650 |

| Doosan PCB Materials Page | Doosan laminate product range | Doosan PCB |

| ECHA SCIP Database | EU SCIP substance-of-concern notifications | echa.europa.eu |

| UL Product iQ | UL flammability certifications lookup | iq.ul.com |

5 FAQs About DS-7409HF Halogen-Free Laminate

Q1: Is DS-7409HF truly halogen-free or just “low-halogen”? It is genuinely halogen-free per IEC 61249-2-21, meaning Cl ≤ 900 ppm, Br ≤ 900 ppm, and total halogens ≤ 1500 ppm. Doosan achieves this through phosphorus/nitrogen-based flame retardants with no brominated compounds in the resin system.

Q2: Can I use DS-7409HF in an automotive application? For most automotive body electronics and functional modules (BCM, lighting, HVAC control), yes. For powertrain, advanced ADAS, or AEC-Q200-qualified components requiring AEC-qualified laminate, you’d want to verify with Doosan on specific automotive qualification status before committing.

Q3: How does the Dk of ~4.5 affect high-speed signal integrity? At 1–3 GHz, it’s perfectly adequate for DDR4/DDR5 interfaces and standard Ethernet up to 10GbE with proper stackup design. Above ~6–8 GHz or for PCIe Gen 5 with tight channel budgets, consider a lower-Dk/Df material.

Q4: Does DS-7409HF require any special storage conditions compared to standard FR-4? Yes, slightly. Halogen-free resins can be more hygroscopic than brominated alternatives. Maintain storage below 60% RH, and pre-bake panels if they’ve been in ambient conditions for more than a week. Check Doosan’s published shelf-life data for your specific thickness/copper weight combination.

Q5: Is DS-7409HF compatible with OSP, ENIG, and HASL finishes? Yes to all three. It is also compatible with ENEPIG and immersion tin. For lead-free HASL, ensure the solder pot temperature profile is controlled tightly — the laminate handles it fine at recommended dwell times, but extended exposure above 265°C should be avoided.

Final Thoughts

The DS-7409HF halogen-free laminate hits a useful middle ground that a lot of designs actually need: solid thermal performance for lead-free assembly, clean RoHS and IEC 61249-2-21 compliance without greenwashing, CTI Group I for high-voltage designs, and a reasonable cost delta over standard FR-4. It’s not exotic, but that’s often exactly the point. For industrial, telecom, and mid-range automotive PCBs, specifying DS-7409HF means your compliance documentation is clean, your fab process is predictable, and you’re not over-paying for performance you don’t need.

If you’re qualifying it for a new design, get the current datasheet direct from Doosan Electro-Materials, cross-reference against IPC-4101 slash sheet requirements for your stackup, and confirm your fab house’s experience with HF materials before committing to production panelization.