Master decoupling capacitor placement, value selection, and PCB layout best practices — with real engineering formulas, ESR/ESL explained, and a practical placement checklist.

Walk into any PCB bring-up session and watch what the first power-on oscilloscope probe checks. Nine times out of ten, it’s the power rail. Unstable voltage, mystery resets, ADC readings that drift for no apparent reason, microcontrollers stuck in brownout — these symptoms are frequently traced back to a missing, misplaced, or incorrectly valued decoupling capacitor. This guide covers every aspect of decoupling capacitors that matters for real-world PCB design: what they actually do at the physics level, how to pick the right values, where to put them in layout, and the placement rules that actually hold up under scrutiny versus the myths that keep getting repeated in forums.

What Is a Decoupling Capacitor and Why Does Every IC Need One?

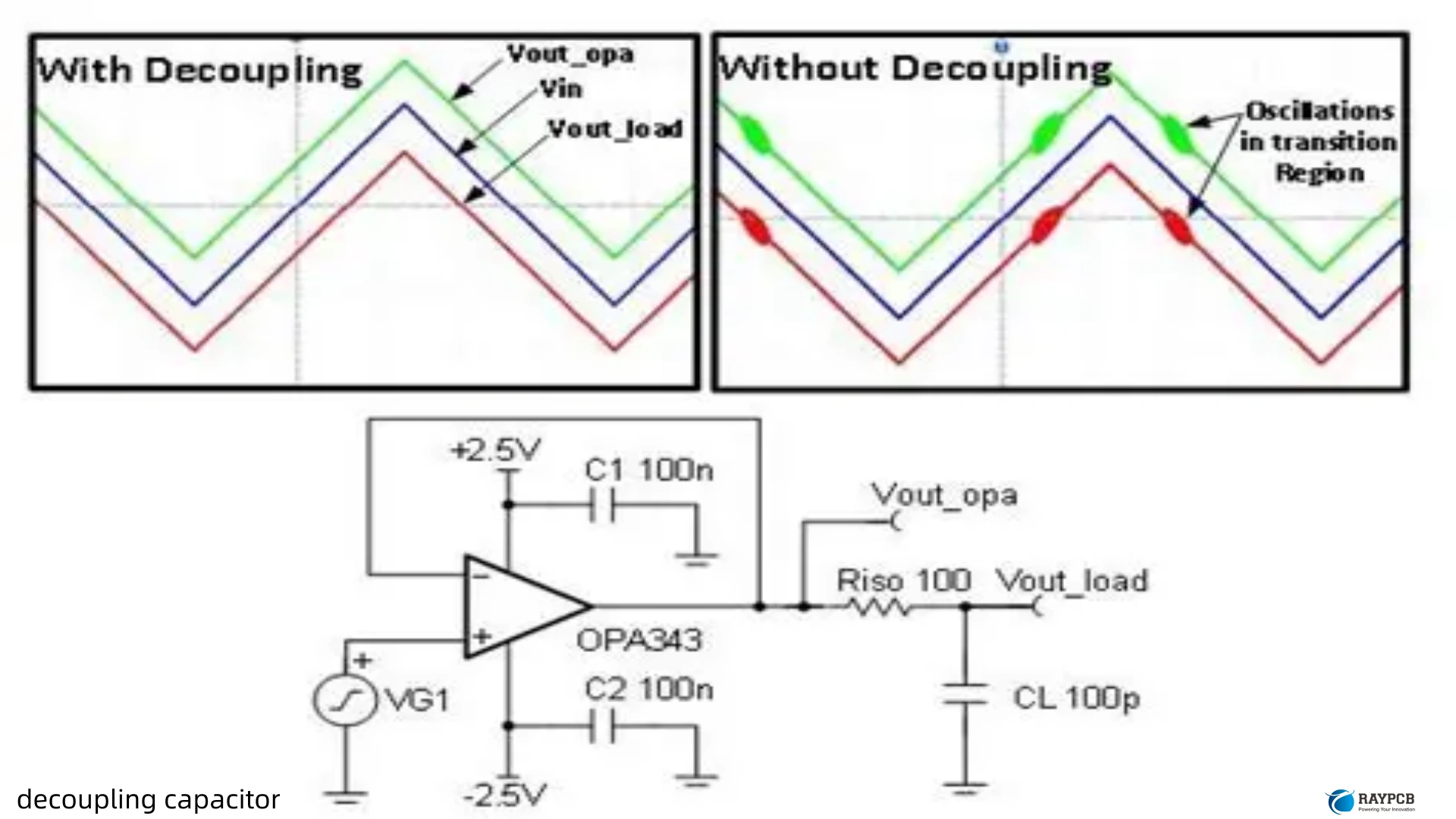

A decoupling capacitor — also called a bypass capacitor in many contexts — is a capacitor placed between an IC’s power supply pin and ground, physically close to the component it serves. Its primary job is to act as a local energy reservoir, storing charge and releasing it rapidly when the IC demands a sudden burst of current during a switching event.

Here is the core problem it solves. When a digital IC switches logic states, it draws a fast transient current spike from the power supply. The PCB traces, vias, and power planes connecting that IC to the main power supply all have inductance. Inductance resists sudden changes in current. So when the IC pulls a spike, the inductance of the supply path creates a temporary voltage dip at the IC’s power pin — a voltage rail sag. If that dip exceeds the IC’s noise margin, you get logic glitches, register corruption, or a full processor reset. Placing a decoupling capacitor directly at the power pin means the capacitor — not the distant power supply — provides that transient current spike. The capacitor’s stored charge bridges the gap while the main supply catches up.

The secondary role of a decoupling capacitor is filtering high-frequency noise already present on the power rail. Every switching power supply produces ripple and high-frequency spectral content. Every digital bus creates simultaneous switching output (SSO) noise. A well-placed decoupling capacitor provides a low-impedance path for this noise to circulate locally rather than coupling into sensitive analog circuits, radiating as EMI, or propagating through the power distribution network (PDN).

Decoupling Capacitor vs. Bypass Capacitor: Is There a Difference?

These terms are often used interchangeably, and in most practical contexts that is fine. Technically, “bypass capacitor” refers to a capacitor that shunts high-frequency noise from an IC’s power pin to ground, while “decoupling capacitor” more precisely refers to a capacitor placed across the power and ground planes to prevent low-frequency rail noise from propagating between sections of the board. In practice, a well-placed 100 nF MLCC near a logic IC serves both functions simultaneously. This guide uses the terms interchangeably, as the industry broadly does.

How a Decoupling Capacitor Works: The Physics Behind It

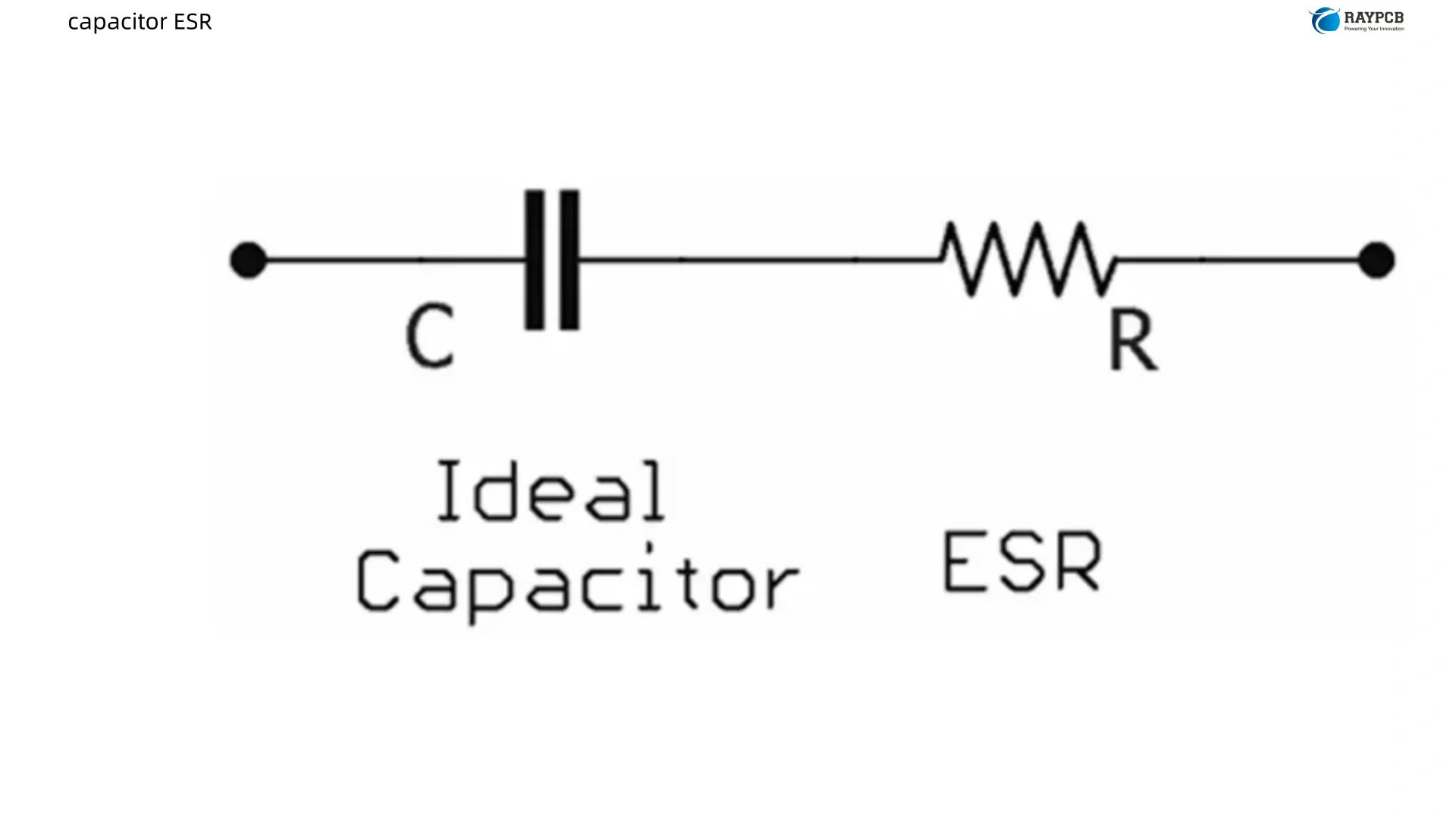

A real capacitor is not an ideal component. It is an RLC network: a capacitor (C) in series with equivalent series resistance (ESR) and equivalent series inductance (ESL). These parasitics fundamentally determine how useful a decoupling capacitor is at any given frequency.

Self-Resonant Frequency (SRF)

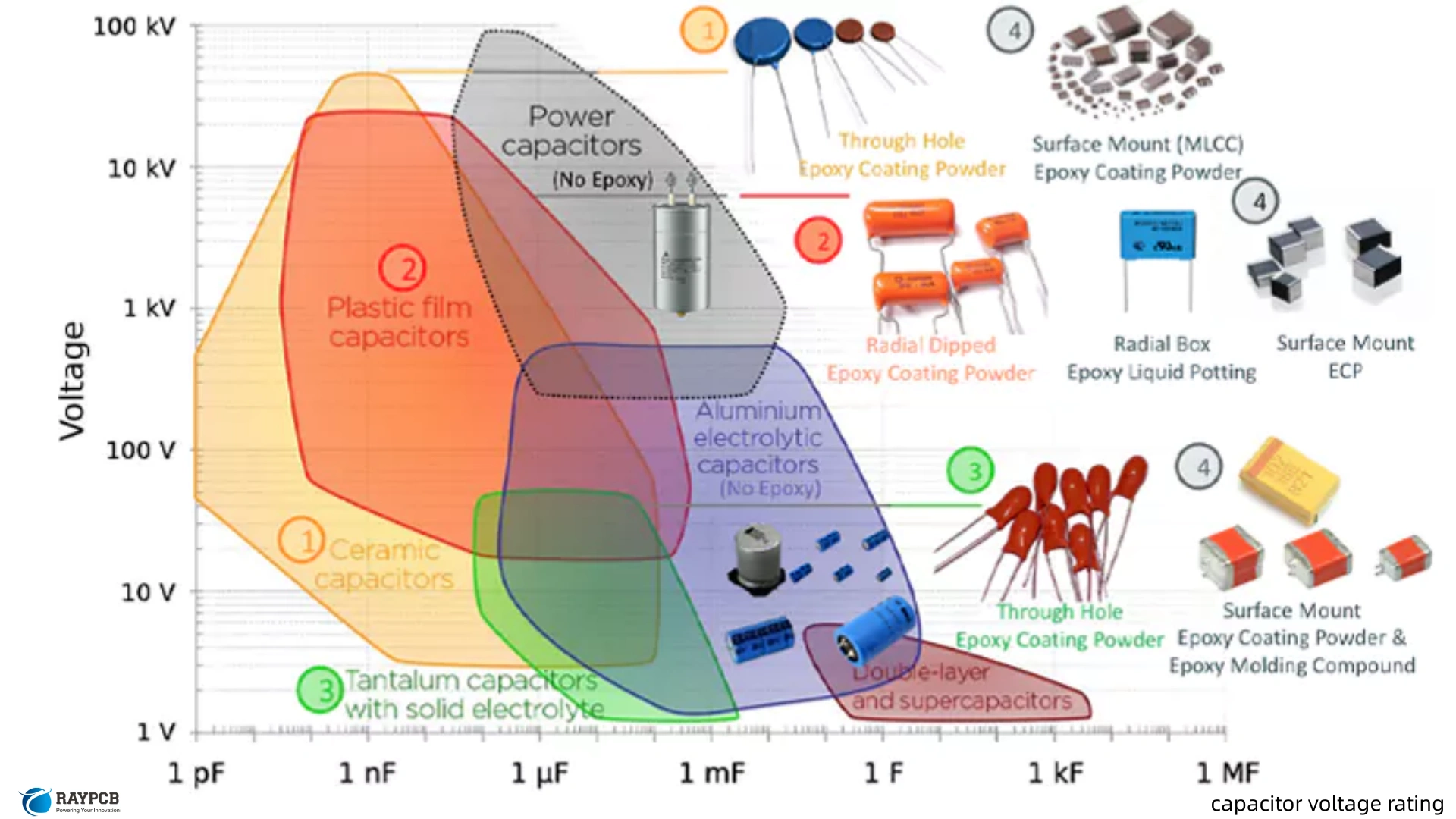

Every decoupling capacitor has a self-resonant frequency (SRF) — the frequency at which the capacitive reactance and the inductive reactance (from ESL) cancel each other out. At the SRF, the capacitor’s impedance reaches its minimum value, which is set by the ESR alone. This is the frequency where the decoupling capacitor is most effective.

Below the SRF: the component behaves as a capacitor — impedance falls as frequency rises. Above the SRF: the ESL dominates — impedance rises as frequency rises, and the component starts behaving like an inductor.

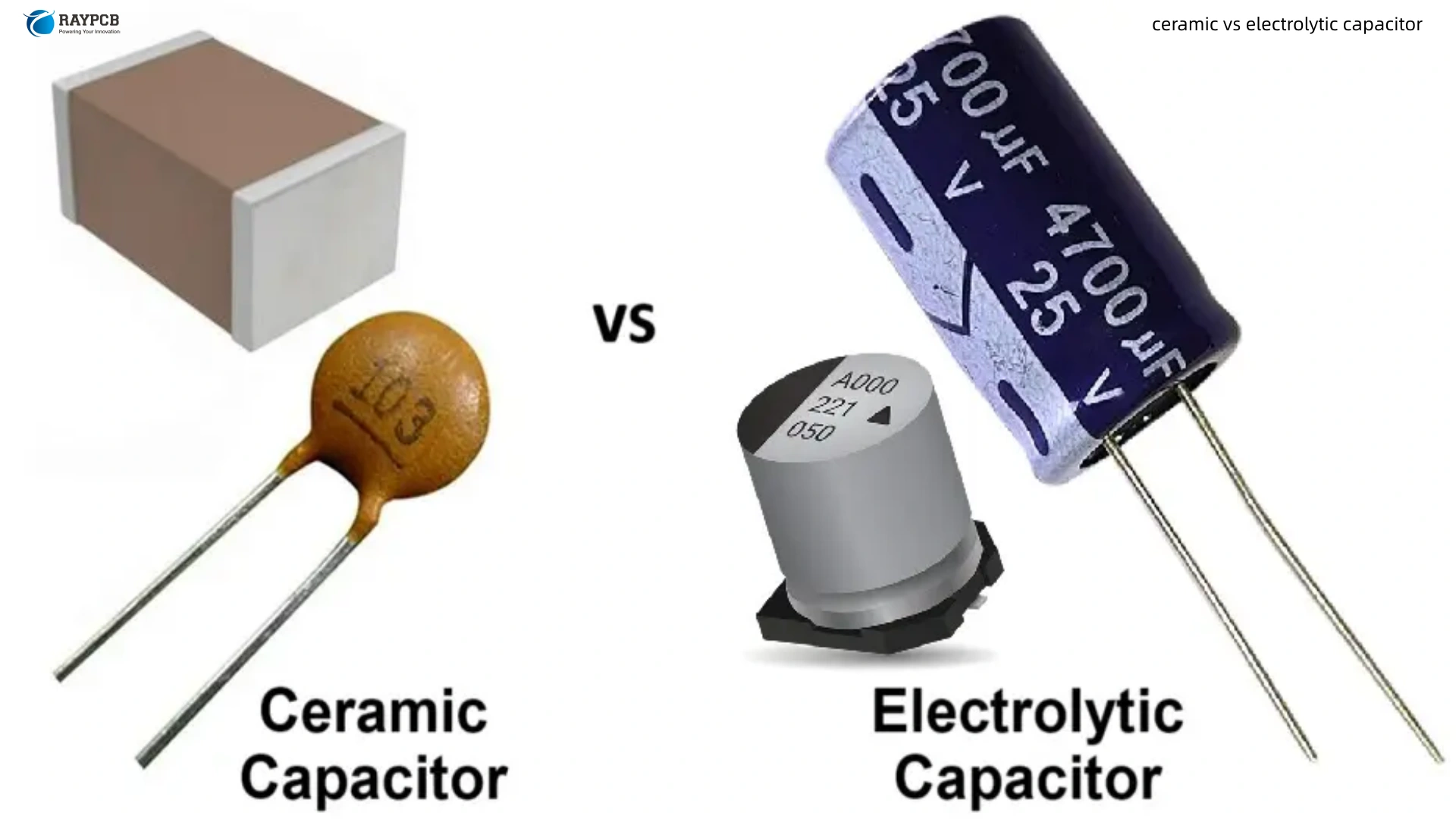

This is why a 100 µF electrolytic capacitor does not help suppress 100 MHz noise. Its SRF might be around 1–2 MHz. At 100 MHz it is already inductive and contributing nothing useful. The correct tool for 100 MHz noise is a small MLCC (e.g., 100 nF or 10 nF in a 0402 package) whose SRF falls in the tens to hundreds of MHz range.

ESR and ESL: What the Datasheet Numbers Actually Mean

ESR (equivalent series resistance) sets the floor for how low the capacitor’s impedance can get at resonance. Lower ESR means lower minimum impedance, which means more effective noise suppression. MLCCs have ESR in the single-digit milliohm range. Aluminum electrolytic capacitors can have ESR of hundreds of milliohms, which is why they are poor choices for high-frequency decoupling despite their large capacitance values.

ESL (equivalent series inductance) determines where the SRF sits and how fast the impedance rises above it. Typical ESL for an 0402 MLCC is around 0.5–1 nH. A through-hole electrolytic can be 10–20 nH. Every millimeter of PCB trace between the capacitor and the IC power pin adds approximately 1 nH of additional mounting inductance on top of the component’s own ESL. A standard via adds another 0.5–1.5 nH depending on board thickness. This is the reason placement matters as much as component selection.

| Capacitor Type | Typical ESR | Typical ESL | SRF Range | Best Decoupling Frequency |

| MLCC 100 nF (0402) | 5–30 mΩ | 0.5–1 nH | 30–150 MHz | 10–200 MHz |

| MLCC 1 µF (0402) | 5–30 mΩ | 0.5–1 nH | 10–50 MHz | 5–100 MHz |

| MLCC 10 µF (0805) | 5–50 mΩ | 1–2 nH | 3–15 MHz | 1–30 MHz |

| Tantalum 10 µF | 100–500 mΩ | 2–5 nH | 1–5 MHz | 100 kHz–5 MHz |

| Al Electrolytic 100 µF | 50–300 mΩ | 10–20 nH | 100–500 kHz | 1 kHz–1 MHz |

| Al Polymer 100 µF | 5–30 mΩ | 5–10 nH | 300 kHz–2 MHz | 10 kHz–5 MHz |

Decoupling Capacitor Values: What to Use and Why

The Classic Three-Tier Decoupling Strategy

Effective decoupling across a wide frequency range requires multiple capacitor values because no single component covers all frequencies well. The industry-standard approach uses three tiers of capacitance placed at different locations in the power distribution hierarchy.

Tier 1 — Bulk Capacitance (10 µF to 100 µF): Large electrolytic, tantalum, or polymer capacitors placed near the power supply entry point on the board or near voltage regulators. These handle low-frequency load transients and provide a charge reservoir for the entire board. They compensate for the slow response time of the main power supply.

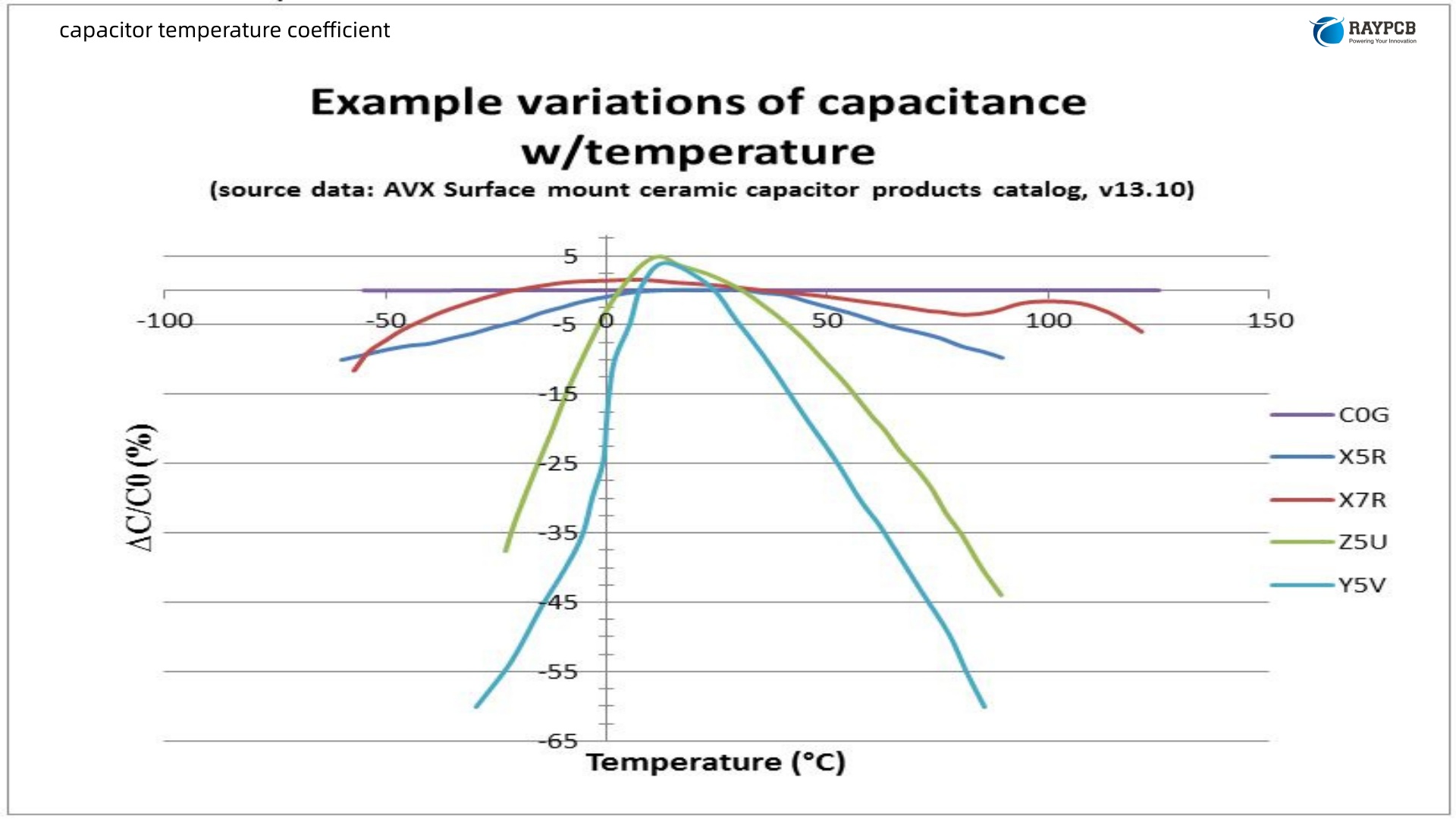

Tier 2 — Mid-Range Decoupling (1 µF to 10 µF): MLCC capacitors (X7R dielectric, 0603 or 0805 package) placed near ICs that have moderate switching currents. These bridge the impedance gap between the bulk caps and the local high-frequency decoupling caps.

Tier 3 — Local High-Frequency Decoupling (100 nF to 10 nF): Small MLCCs (0402 or 0201 package, X7R dielectric) placed directly at each IC power pin. These handle fast switching transients and high-frequency noise at the component level. The 100 nF (0.1 µF) value is the most universal starting point in digital design and is the standard recommendation from virtually every MCU and FPGA manufacturer.

How Many Decoupling Capacitors Per IC?

The standard rule is one 100 nF MLCC per VDD/VCC power pin, supplemented by one shared mid-range capacitor (1–10 µF) per IC. For simple microcontrollers with two or three power pins, this means three to four capacitors per IC. For large FPGAs with dozens of power pins across multiple supply domains, a full decoupling plan following the manufacturer’s application notes is required — these documents usually specify values, quantities, and placement constraints precisely.

An important nuance: if space prevents one capacitor per pin, use a minimum of one 100 nF cap per IC, placed at the power pin cluster that drives the highest-speed internal logic. Shared capacitors are a compromise but are better than no local decoupling.

Calculating Decoupling Capacitance from First Principles

For engineers who need to go beyond rules of thumb, the minimum required capacitance can be estimated from the transient current demand:

C = I × Δt / ΔV

Where:

- I = the transient current demand of the IC (from the datasheet or simulation)

- Δt = the rise/fall time of the switching transient

- ΔV = the maximum acceptable voltage droop at the power pin (typically 5% of VDD)

Example: A microcontroller draws a 100 mA transient spike with a 10 ns rise time, and the supply is 3.3 V with a maximum 5% droop (165 mV allowed).

C = 0.1 A × 10 × 10⁻⁹ s / 0.165 V ≈ 6 nF

Two parallel 100 nF capacitors significantly exceeds this requirement and also provides lower effective ESL than a single larger cap — good margin for most MCU applications.

Decoupling Capacitor Value Selection by Application

| Application | Recommended Local Decoupling | Supplemental Bulk Cap |

| 3.3V / 5V Logic MCU | 100 nF X7R MLCC per VDD pin | 10 µF X7R or polymer |

| FPGA Core Voltage | 100 nF + 10 nF per power pin cluster | Per vendor app note |

| High-Speed SerDes / DDR | 100 nF + 1 nF per power pin | 100 µF polymer near rail |

| Op-Amp Supply Pin | 100 nF C0G + 10 µF tantalum | — |

| RF IC Supply | 100 pF + 10 nF + 100 nF cascaded | 10 µF near LDO output |

| Motor Driver VCC | 100 nF MLCC + 100 µF electrolytic | 220–470 µF bulk near driver |

| Audio DAC/ADC AVDD | 100 nF C0G (low noise) | 10 µF low-ESR tantalum |

Decoupling Capacitor Placement: The Rules That Actually Matter

Placement is where theory meets the reality of a physical PCB, and it is where more designs fall short than in value selection. Correct component selection with poor placement delivers worse results than decent component selection with excellent placement.

The First Law of Decoupling: Minimize Loop Inductance

The single most important placement objective is minimizing the inductance of the current loop formed by the IC power pin, the capacitor, and the return path back through ground. Every element in that loop adds inductance: trace length, via height, trace width, the gap between power and ground vias. Every nanohenry of loop inductance reduces the frequency range over which the capacitor is effective.

A practical trace inductance rule: approximately 1 nH per millimeter of trace length on a typical PCB. This means a decoupling capacitor placed 5 mm away from the IC power pin, with traces routing to reach it, has already added 5 nH of mounting inductance before the capacitor’s own ESL is even counted. At 100 MHz, 5 nH of inductance presents an impedance of over 3 Ω — completely defeating any benefit from the capacitor.

The target: place decoupling capacitors within 1–2 mm of the IC power pin they serve, with the shortest possible trace routing to both power and ground connections.

Placement Strategy by PCB Stack-Up

The effectiveness and optimal placement strategy for decoupling capacitors changes depending on the PCB layer arrangement.

PCBs with tightly coupled power and ground planes (≤ 4 mil / 0.1 mm separation): The interplane capacitance of closely spaced copper planes is significant — approximately 16 pF/cm² for FR-4 at 10 mil spacing, increasing as planes get closer. On a board with tight plane spacing, the planes themselves provide high-frequency decoupling and the exact X/Y position of the discrete capacitors becomes less critical. The parasitic inductance of the plane structure is inherently low and uniformly distributed. This is how dense server motherboards manage to use relatively few bypass capacitors while supporting GHz-class processors.

Typical 4-layer PCBs with standard stack-up (40–60 mil plane separation): The wide interplane gap makes plane capacitance negligible. Discrete capacitor placement is critical. One capacitor per power pin, placed as close as physically possible, is required for reliable operation at high clock speeds.

Two-layer PCBs (no dedicated power planes): Decoupling capacitor placement is critical and the ground return path must be deliberately routed. Use the shortest possible traces, keep the capacitor and IC power pin on the same layer, and route a direct wide trace to the capacitor ground pad and back to the main ground reference. A solid ground pour beneath the decoupling network helps significantly.

Via Placement: The Often-Overlooked Detail

Many engineers get the capacitor placement correct but then add unnecessary inductance through careless via routing. The best practice for connecting a decoupling capacitor to buried power and ground planes:

- Place the power via and the ground via adjacent to the capacitor pads — not at the end of a trace stub running from the pad

- Keep the power and ground vias as close together as possible — the distance between them determines the loop area of the current return path through the planes

- For BGA packages and dense high-speed designs, consider via-in-pad technology to eliminate trace stubs entirely and connect directly to the power ball through the pad

- Avoid routing any traces between the capacitor pad and the via — the via should be at the edge of the pad or immediately next to it

- Use multiple vias per capacitor pad in high-current or high-frequency applications to reduce via inductance in parallel

The Back-Side Placement Technique for BGAs

For BGA packages on multilayer PCBs, placing the decoupling capacitor on the opposite (bottom) side of the PCB directly beneath the BGA can achieve lower loop inductance than placing the capacitor on the top side next to the BGA. The current path from a BGA power ball on the top layer, down through a short via to the bottom-side capacitor, and back through a ground via is often shorter than routing across the top surface to a nearby capacitor. This technique requires via-in-pad or very short stubs on the top side ball pads and is standard practice in high-speed processor board design.

Component Placement Order: Capacitors Before Traces

This sounds obvious but it gets ignored in real design schedules. Place decoupling capacitors before routing any signal traces. Decoupling capacitors should be treated as extensions of the IC package — they belong physically next to the power pins with guaranteed clear routing space. When signal traces are routed first and capacitors are fitted into leftover space, the result is always a layout compromise. The decoupling capacitors end up further away than optimal, connected through convoluted trace paths, and their effectiveness degrades accordingly.

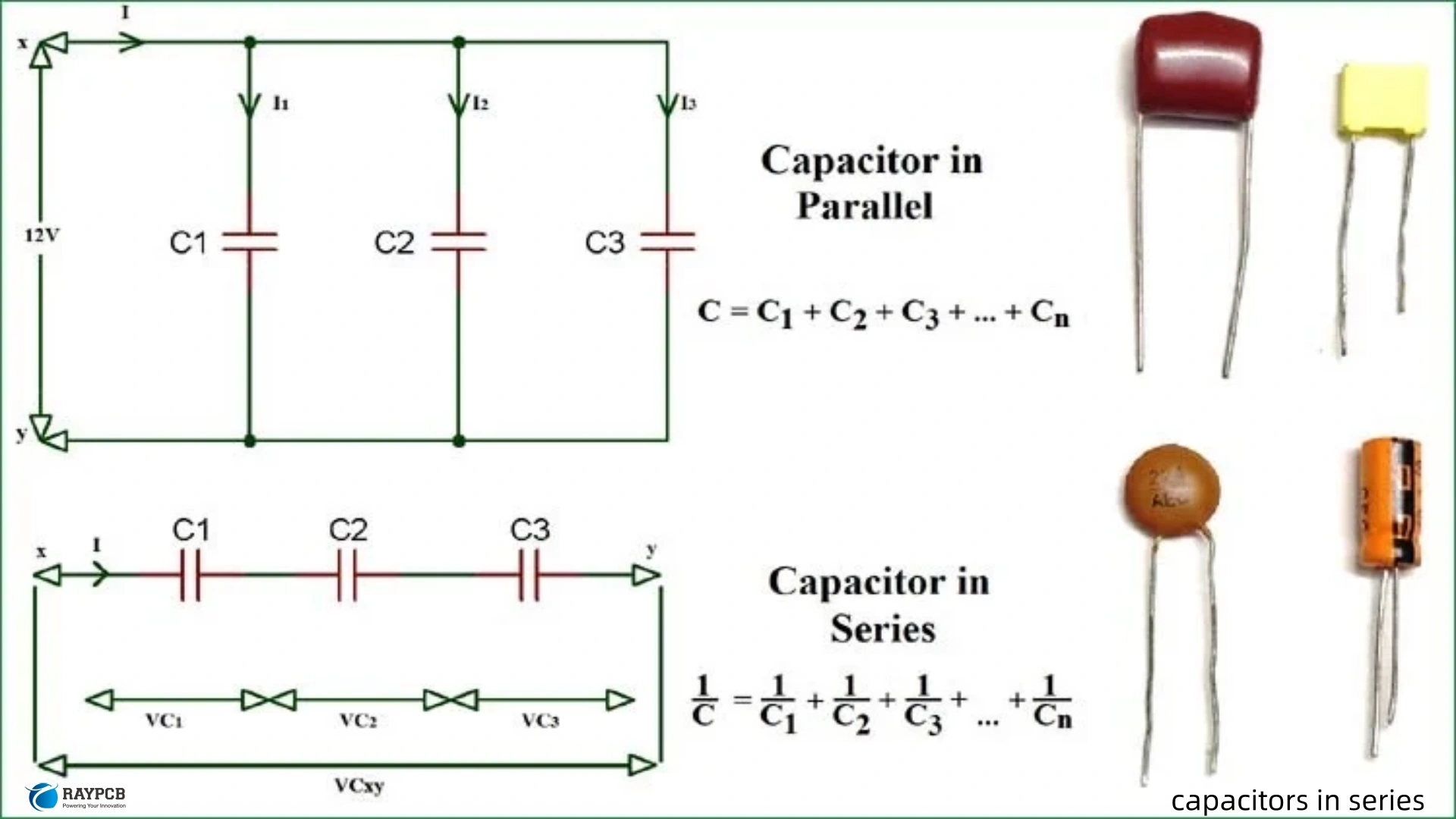

Multiple Capacitors in Parallel: Value Ordering

When using multiple decoupling capacitors of different values on the same power pin — for example, a 100 nF and a 10 nF in parallel — a common question is which capacitor should be closest to the IC. The answer: place the smallest-value capacitor closest to the power pin. The smaller capacitor has a higher SRF and handles the fastest transient currents. It needs the lowest mounting inductance to do its job effectively. The larger capacitor can be slightly further away because it handles slower, lower-frequency transients where a few extra millimeters of trace inductance matters much less.

A caution on anti-resonance: placing two different-value capacitors in parallel creates an anti-resonance peak (impedance spike) at a frequency between the SRFs of the two capacitors. If this peak falls at a critical frequency in your design — such as a major clock harmonic — the parallel combination can actually increase PDN impedance at that frequency. In sensitive designs, use simulation tools to check the parallel impedance profile before committing to the layout.

Common Decoupling Mistakes PCB Engineers Make

Using Electrolytics for High-Frequency Decoupling

An aluminum electrolytic capacitor with 10 nH ESL and a SRF below 500 kHz contributes almost nothing to decoupling at 50 MHz or above. It is the correct choice for bulk energy storage on a power rail, but it should always be supplemented by ceramic MLCCs for local high-frequency bypass. Using only electrolytics near a high-speed IC is one of the most common mistakes in beginner PCB designs.

Putting Decoupling Capacitors on the Wrong Side of Ferrite Beads

If a ferrite bead separates the noisy digital supply from a clean analog supply, the decoupling capacitors for the analog section must be placed after the ferrite bead — on the clean side. Placing them before the ferrite bead means they decouple the noisy digital rail. The whole point of the ferrite bead filter is undermined if the downstream decoupling is missing.

Daisy-Chaining Power Connections Through Capacitor Pads

Some designers route the main power trace through the capacitor pad — the trace runs from the power source, to one pad of the capacitor, continues to the next capacitor pad, and then finally reaches the IC power pin. This series routing means the decoupling capacitor is connected in series with the power path rather than in shunt (parallel) between power and ground. A shunt bypass capacitor must connect from the power node to ground — not in line between the source and the load.

Ignoring the IC Manufacturer’s Application Note

Every IC manufacturer publishes reference designs and application notes for their products. For high-speed processors, FPGAs, and RF ICs, these documents specify not just capacitor values but exact placement constraints, recommended via structures, and bill of materials. Following these recommendations is free high-quality design guidance. Ignoring them in favor of general rules of thumb — when the manufacturer has done the measurements — is a source of unnecessary risk.

Single Decoupling Cap for Multiple Power Pins

Some MCUs have three VDD pins and three GND pins for a reason — each pin supplies a different internal circuit block. Sharing a single 100 nF capacitor across all three VDD pins, placed somewhere between them, compromises the decoupling for all three. Each power pin deserves its own capacitor, placed directly at that pin.

Decoupling Capacitors for Specific Circuit Types

Analog and Mixed-Signal ICs

Analog circuits — op-amps, ADCs, DACs, voltage references — are sensitive to power supply noise in ways that digital logic is not. For analog power pins, use C0G/NP0 dielectric MLCCs rather than X7R for the local high-frequency bypass capacitor. C0G’s lower dielectric absorption, non-piezoelectric behavior, and stable capacitance under bias make it superior for keeping precision analog supply pins clean.

A low-noise LDO before the analog supply rail, followed by a 10 µF low-ESR tantalum and a 100 nF C0G at each analog power pin, is a solid baseline for precision measurement circuits.

FPGA and High-Speed Processor Decoupling

FPGAs require decoupling across a wide frequency range because internal logic switches simultaneously across millions of flip-flops. Core voltage decoupling for a mid-size FPGA can require dozens of capacitors — 100 nF and 10 nF in combination per power pin cluster. Always start with the official power delivery application note from the FPGA vendor (Xilinx/AMD, Intel/Altera, Lattice). These documents are detailed and board-specific.

RF and Microwave Circuits

RF supply decoupling uses a cascaded approach: a large bulk cap (10 µF tantalum or polymer) at the regulator output, followed by progressively smaller ceramics (1 µF → 100 nF → 10 nF → 100 pF) as you approach the RF IC power pin. The 100 pF value has an SRF in the low GHz range and handles GHz-frequency supply noise directly at the IC. The cascade creates overlapping low-impedance bands that together cover from kHz to multi-GHz frequencies.

Decoupling Capacitor Best Practices: Quick Reference

| Design Step | Best Practice |

| Value selection | 100 nF X7R MLCC per digital IC power pin; supplement with 1–10 µF per IC |

| Package size | Use 0402 or 0201 for lowest ESL; avoid 0805 or larger for local bypass |

| Dielectric (analog) | Use C0G/NP0 for precision analog and audio supply pins |

| Placement | Within 1–2 mm of IC power pin; on back side of PCB for BGAs |

| Via placement | Power and ground vias directly adjacent to capacitor pads |

| Trace routing | Shortest possible traces; wide and direct; no stubs |

| Ordering | Smallest value cap closest to power pin when stacking multiple values |

| Stack-up | Tighter plane spacing reduces placement sensitivity for high-freq decoupling |

| Manufacturer guidance | Always check and follow the IC vendor’s decoupling application note |

| Simulation | Use PDN simulation for FPGA/high-speed designs to verify impedance profile |

| Placement timing | Place decoupling caps before routing signal traces |

| Ferrite beads | Place decoupling capacitors on the clean side of EMI filters |

Frequently Asked Questions

Q1: Can I place my decoupling capacitor far from the IC as long as I use large traces?

No. Trace inductance is dominated by trace length, not trace width, once the width is reasonably wide (above 10 mils for most PCBs). A trace that is twice as wide has roughly half the inductance per unit length — but a trace that is twice as long has twice the inductance regardless of width. The only way to reduce mounting inductance is to shorten the distance between the capacitor and the IC power pin. Wide traces help marginally; short traces help fundamentally.

Q2: Do I need decoupling capacitors if I have a solid, continuous ground plane?

Yes. A good ground plane improves the return path and reduces the loop inductance of the current path, making your decoupling capacitors more effective. But the ground plane does not replace the need for discrete decoupling capacitors. The plane does not store charge in the way a capacitor does, and it cannot supply the instantaneous transient current spikes that digital ICs demand. Both are needed — the ground plane and the discrete capacitors work together.

Q3: My schematic shows 100 nF next to every IC. Does the value matter, or is it just symbolic?

The value matters for frequency coverage. 100 nF has a practical SRF in the range of 30–100 MHz in a typical 0402 package, making it effective for the switching frequencies of most digital logic. For very high-speed circuits (>100 MHz clock domains, GHz SerDes), supplement with a 10 nF or 1 nF capacitor at those specific power pins. For slower MCUs below 50 MHz, 100 nF is usually sufficient as the local bypass without the additional smaller value.

Q4: Why do some IC application notes call for 10 nF and 100 nF in parallel rather than a single 110 nF capacitor?

Because two capacitors with different values have different SRFs and therefore cover different frequency ranges. A 100 nF has its SRF at a lower frequency than a 10 nF. Placing them in parallel creates two impedance minima — one around the SRF of each capacitor — giving broader frequency coverage than a single 110 nF. A single 110 nF capacitor only has one SRF, somewhere between the two, and covers neither frequency band as effectively. The parallel combination also reduces total ESL (two sets of vias in parallel).

Q5: My board has reset problems under high CPU load. Could it be a decoupling issue?

Very likely. Classic symptoms of inadequate power decoupling include: microcontroller resets or hangs under heavy processing load, ADC readings that shift when digital activity increases, oscilloscope measurements showing rail voltage drooping or spiking in time with processor activity, and EMC test failures in the radiated emissions band. Start by probing the IC’s VDD pin directly with a 10:1 probe tip soldered as close to the pin as possible (not through a clip lead). If you see voltage excursions exceeding 5% of VDD correlated with the resets, insufficient or improperly placed decoupling is the likely cause. Add 100 nF MLCCs directly at the VDD pins and retest.

Useful Resources for Decoupling Capacitor Design

| Resource | Description | Link |

| Murata SimSurfing | Simulate MLCC capacitance, ESR, ESL vs. frequency, temperature, and DC bias | ds.murata.co.jp/simsurfing |

| KEMET KSIM | Model capacitor impedance with real parasitics under operating conditions | ksim3.kemet.com |

| TDK MLCC Selector | Filter MLCC by capacitance, voltage, case size, dielectric, ESR | product.tdk.com |

| AVX (Kyocera) SpiCap | Download SPICE models for AVX MLCCs for PDN simulation | avx.com |

| Digi-Key MLCC Filter | Full parametric search including ESR, ESL, SRF fields | digikey.com |

| Altium PDN Analyzer | Integrated PDN simulation and impedance profiling within Altium Designer | altium.com |

| Cadence Sigrity PowerSI | Industry-standard PDN analysis and decoupling optimization tool | cadence.com |

| Würth Elektronik Redexpert | Interactive MLCC impedance and frequency response tool with real component data | we-online.com/redexpert |

| Speeding Edge (Lee Ritchey) | Technical papers on PDN design, plane capacitance, and decoupling strategy | speedingedge.com |

| IPC-2141A | Standard for high-speed board design including power distribution guidelines | Available via IPC.org |

Summary

The decoupling capacitor is one of the most consequential passive components in any digital or mixed-signal PCB design, and also one of the most frequently mishandled. The guiding principles:

Every IC power pin needs a local 100 nF X7R MLCC placed as close as physically possible to the pin. Supplement with a 1–10 µF mid-range capacitor per IC and a 100 µF bulk capacitor near the power entry or voltage regulator. Use additional small-value capacitors (10 nF, 1 nF) at high-speed power pins where clock frequencies exceed 100 MHz.

Placement matters as much as value selection. Every millimeter of trace between the capacitor and the IC power pin adds ~1 nH of mounting inductance, which directly degrades high-frequency decoupling effectiveness. Place capacitors before routing signal traces. Put vias directly at capacitor pads. Use the back side of the PCB for BGA packages.

Always check the IC manufacturer’s application note for specific decoupling recommendations. For FPGAs, high-speed processors, and RF ICs, the vendor’s power delivery guide is the most accurate source of capacitor values, quantities, and placement rules — more reliable than any generic rule of thumb.

Get the decoupling right, and your first power-on oscilloscope measurement will show clean, stable rails. Get it wrong, and the same measurement will explain a lot of debugging sessions you thought were software problems.