CTE PCB substrate guide: Compare FR-4, polyimide, Rogers, and ceramic CTE values, understand failure modes, and learn design strategies to prevent thermal expansion failures.

Every PCB engineer has been there — you assemble a board that tests perfectly at room temperature, only to watch it fail in the field after a few hundred thermal cycles. Nine times out of ten, CTE mismatch is the culprit. Understanding CTE PCB substrate behavior isn’t just academic theory; it’s the difference between a product that ships reliably and one that generates expensive warranty returns.

This guide breaks down exactly what CTE is, why substrate selection is critical, how different materials compare, and what you can do in your layout to fight back against thermal expansion failures.

What Is CTE in a PCB Substrate?

CTE, or Coefficient of Thermal Expansion, is the rate at which a material expands (or contracts) as its temperature changes. In PCB design, it’s expressed in parts per million per degree Celsius (ppm/°C) — meaning for every 1°C rise in temperature, a material with a CTE of 15 ppm/°C will expand by 15 micrometers per meter of length.

Every material in your PCB stack-up has its own CTE value, and they’re rarely the same. Copper, which forms your traces and plating, expands at roughly 16–17 ppm/°C. Standard FR-4 laminate runs about 11–18 ppm/°C in the X/Y plane, but its Z-axis CTE tells a very different — and more dangerous — story.

X/Y vs. Z-Axis CTE: Why the Distinction Matters

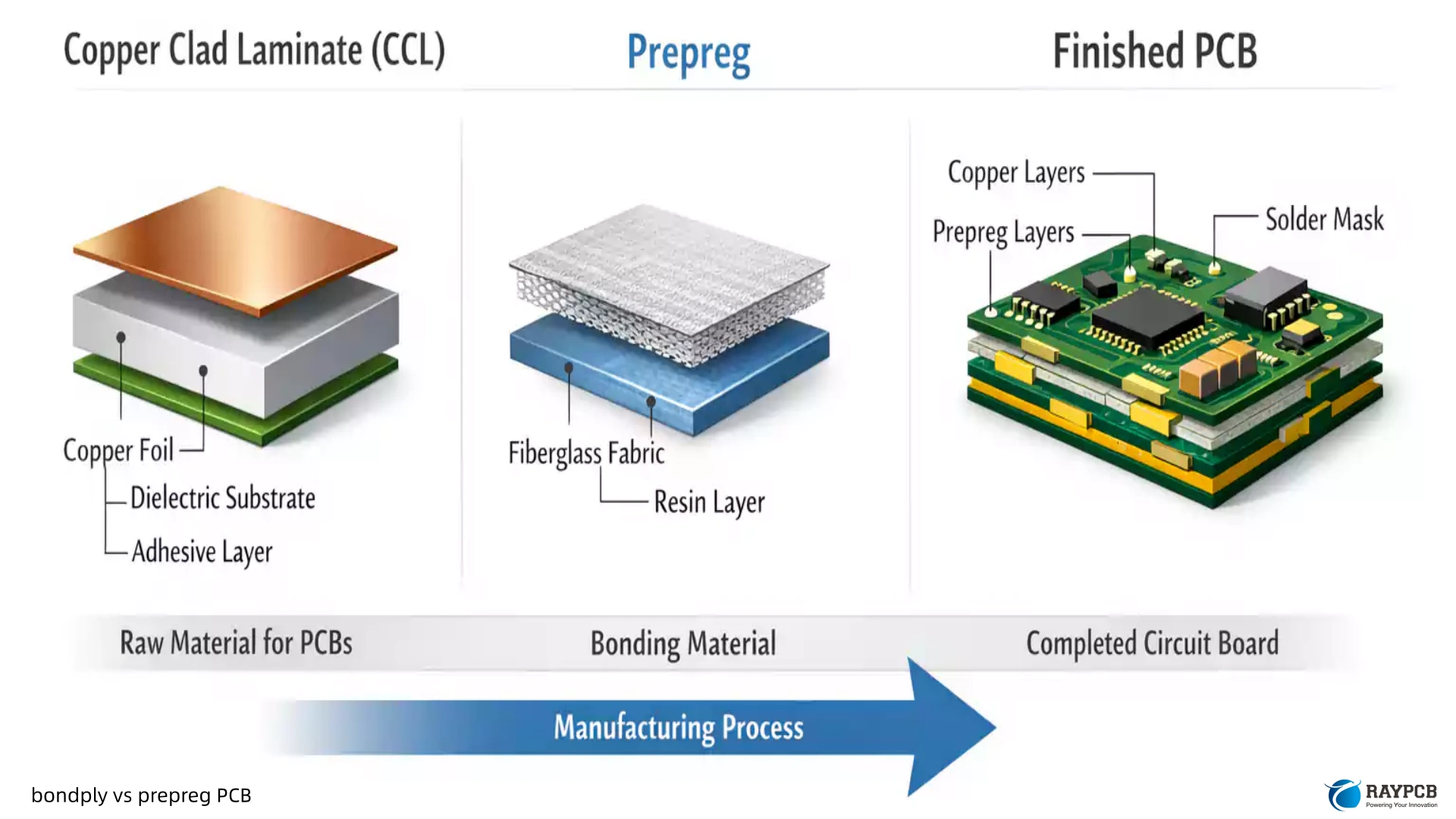

PCB substrates behave anisotropically when it comes to thermal expansion — that is, they expand differently depending on the axis. This is largely because woven fiberglass reinforcement constrains the laminate in the X and Y directions. The glass cloth does its job in-plane, so X/Y CTE values tend to stay relatively manageable (10–20 ppm/°C for most laminates).

The Z-axis, however, has no such reinforcement. The resin system alone determines out-of-plane expansion, and for standard FR-4, Z-axis CTE can hit 55–70 ppm/°C — more than four times the value of copper. When you consider that a plated through-hole barrel is essentially a column of copper stretching the full thickness of the board, it becomes clear why Z-axis CTE is the primary driver of PTH barrel cracking and via failures.

A practical target: aim for below 70 ppm/°C in the Z-axis for standard designs. High-reliability applications, particularly those involving lead-free assembly with peak reflow temperatures approaching 260°C, demand even tighter control.

Why CTE Mismatch Is a Reliability Time Bomb

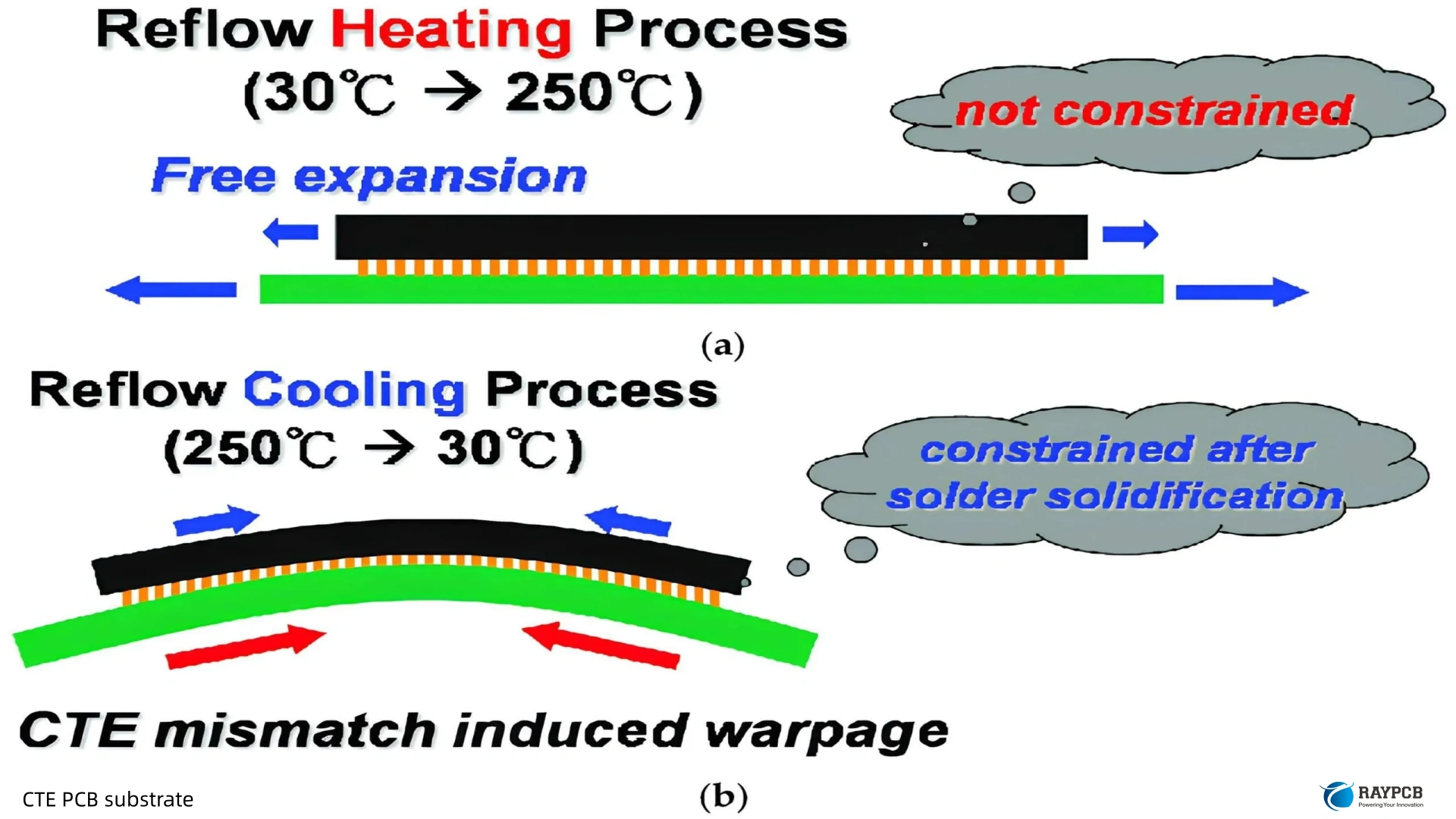

A single thermal excursion rarely causes catastrophic failure on its own. The real danger is thermal cycling — repeated heating and cooling that accumulates mechanical stress in copper structures, solder joints, and substrate interfaces. Think of it like bending a paper clip back and forth: each cycle doesn’t break it, but eventually fatigue sets in.

Plated Through-Hole (PTH) Barrel Cracking

This is the classic CTE failure mode in multilayer boards. The Z-axis CTE mismatch between the copper plating (~17 ppm/°C) and the FR-4 substrate (~55–60 ppm/°C) subjects PTH barrels to enormous cyclic strain. Every time the board heats up, the substrate expands far more than the copper barrel can accommodate. Over hundreds or thousands of cycles, this initiates cracks in the barrel wall — often at the mid-span or at the interface with inner layers. The result is intermittent continuity that’s maddeningly difficult to reproduce at room temperature during debug.

High aspect ratio vias (typically 8:1 or greater) are especially vulnerable. Thicker plating or via-fill copper can mitigate the problem, but material selection remains the best first line of defense.

BGA and Surface Mount Solder Joint Fatigue

When a ceramic chip carrier (CTE ≈ 6 ppm/°C) sits on standard FR-4 (CTE ≈ 15–18 ppm/°C in X/Y), every thermal cycle shears the solder joints. Large components like BGAs amplify this effect because corner joints must absorb the cumulative displacement over a larger footprint. The joints work-harden over time and eventually crack — often beginning at the corner balls of a BGA array where the thermal displacement is greatest.

Lead-free solder alloys, now mandated in most markets, are actually less ductile than tin-lead solders, which makes CTE mismatch management even more critical than it was in the SnPb era.

Delamination and Pad Lifting

Extreme Z-axis expansion puts direct tensile stress on the bond between copper planes and the substrate resin. If absorbed moisture vaporizes rapidly during reflow (the “popcorn” effect), or if the thermal excursion approaches the glass transition temperature (Tg), this stress can physically separate the copper from the laminate. Pad lifting and inter-layer delamination are often terminal failure modes that render the board unrepairable.

The Role of Tg in CTE Behavior

Glass transition temperature (Tg) and CTE are deeply interconnected. Below Tg, a polymer-based substrate is in its rigid, glassy state — CTE values are relatively controlled. Once the material crosses Tg, the resin transitions to a softer, rubbery state and the CTE — especially in the Z-axis — increases steeply. For standard FR-4, Tg is around 130°C; high-Tg variants push this to approximately 170°C.

The practical implication: if your board routinely operates near or above its substrate’s Tg, you’re running in a regime where Z-axis expansion accelerates sharply, dramatically increasing stress on vias and conductors. Lead-free reflow processes, which push temperatures to 250–260°C, briefly exceed the Tg of standard FR-4 during every assembly pass. This is why high-Tg laminates are now essentially the default for most production designs.

Note that Tg is reversible — the material returns to its glassy state when it cools below Tg. Decomposition temperature (Td) is the point of irreversible chemical breakdown, which is typically above 300°C for standard laminates. You never want to see Td during normal operation.

CTE Values for Common PCB Substrate Materials

Understanding how different substrate materials compare on CTE is essential before making a material selection decision. The table below consolidates typical values from published datasheets across commonly used PCB laminates.

Table 1: CTE Comparison of Common PCB Substrate Materials

| Material | X/Y CTE (ppm/°C) | Z-Axis CTE (ppm/°C) | Tg (°C) | Typical Use Case |

| Standard FR-4 | 11–18 | 55–70 | 130–140 | General-purpose consumer/industrial |

| High-Tg FR-4 | 11–15 | 50–65 | 150–175 | Industrial, multi-layer, lead-free assembly |

| Polyimide | 12–16 | 50–60 | 250–260+ | Aerospace, flex, high-temperature |

| PTFE (Rogers, Taconic) | 17–24 | 24–50 | — | RF, microwave, high-frequency |

| Rogers RO4350B | 11–14 | ~32 | >280 (Td) | RF, cellular, radar |

| Ceramic (Al₂O₃) | 6–7 | 6–7 | N/A (inorganic) | Power electronics, high-reliability |

| Aluminum Nitride (AlN) | 4.3–5.8 | 4.3–5.8 | N/A (inorganic) | High-power, LED, automotive |

| Copper (conductor) | ~17 | ~17 | N/A | Traces, planes, plating |

| Silicon (chip) | ~2.6 | ~2.6 | N/A | Die-level reference |

Values are approximate and vary by manufacturer and specific grade. Always verify against laminate supplier datasheets for design sign-off.

The ceramic entries stand out immediately — at 4–7 ppm/°C, they approach the CTE of silicon (~2.6 ppm/°C), which is why ceramics are favored for bare-die mounting and power module applications where direct die-attach is involved. The flip side is that ceramic substrates are brittle, expensive, and require specialized manufacturing processes.

Substrate-Specific CTE Profiles: What Each Material Means in Practice

FR-4 and High-Tg FR-4

FR-4 remains the workhorse of the industry for very good reasons: it’s cost-effective, widely available, and well-characterized. But its Z-axis CTE of 55–70 ppm/°C demands respect. For boards with through-holes above 6:1 aspect ratios, multiple reflow cycles, or operating environments above 85°C, consider upgrading to a high-Tg variant such as Isola IS410, Panasonic Megtron 6, or Isola FR408HR. These materials keep Tg in the 170–190°C range, giving you significantly more Z-axis dimensional stability through reflow.

Polyimide

Polyimide substrates (DuPont Kapton being the most recognized film) offer Tg values above 250°C and Z-axis CTE of around 50–60 ppm/°C — comparable to high-Tg FR-4 on the Z-axis, but with dramatically better performance at elevated temperatures. Polyimide is essentially the default for aerospace, military, and flex PCB applications. The trade-off is higher material cost and a tendency for moisture absorption, which requires pre-baking before assembly.

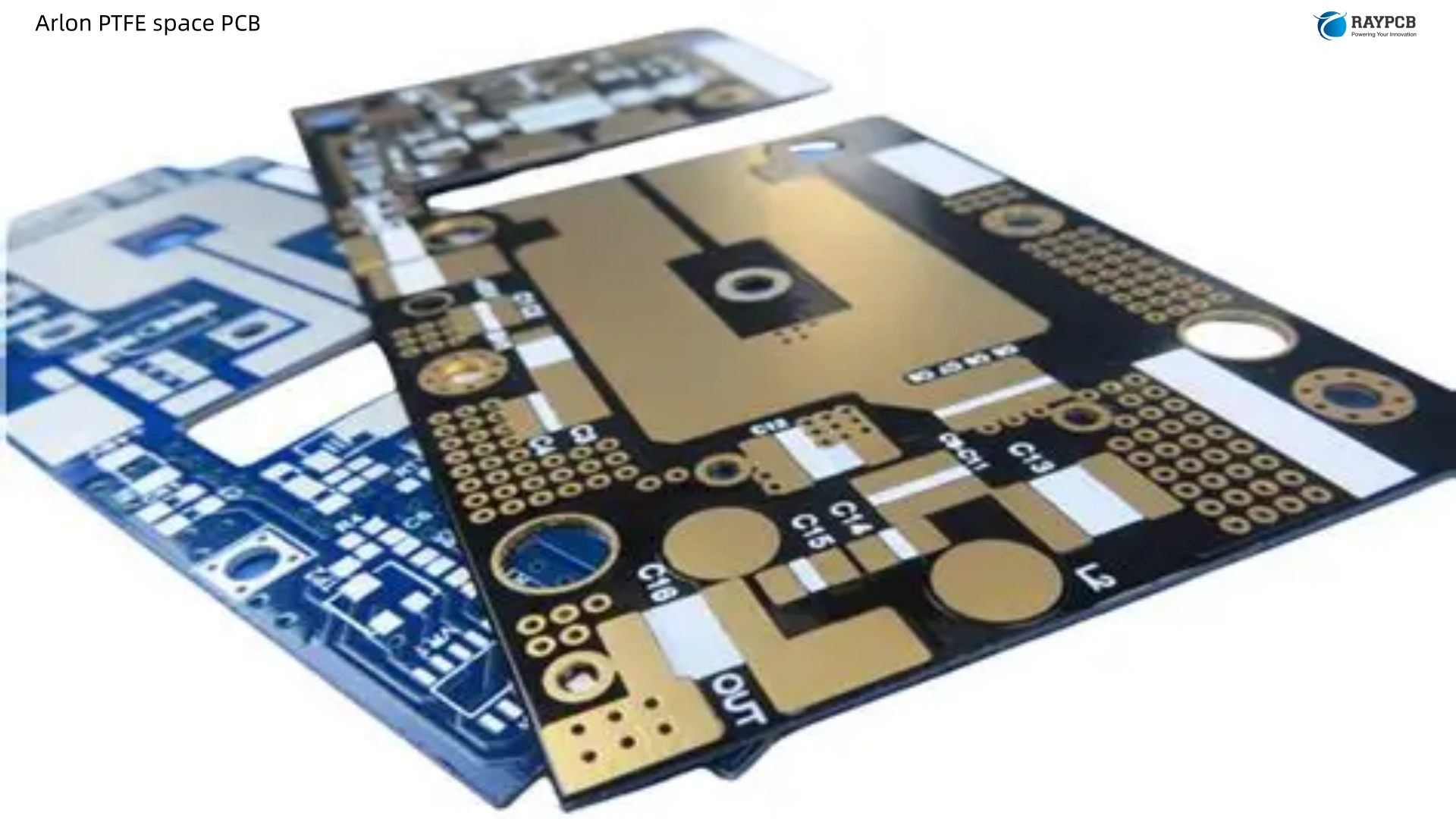

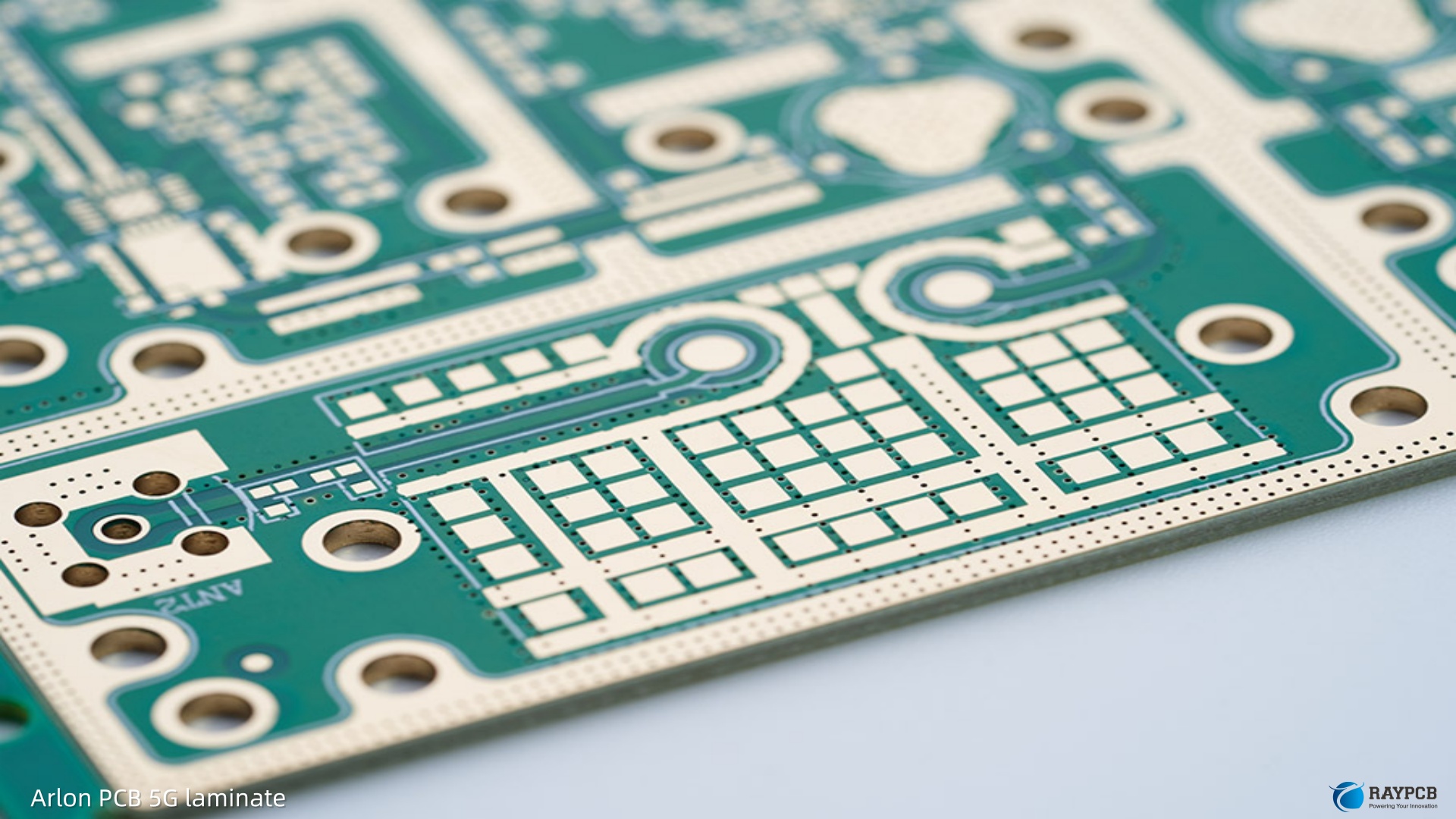

PTFE-Based Laminates (Rogers, Taconic, Isola)

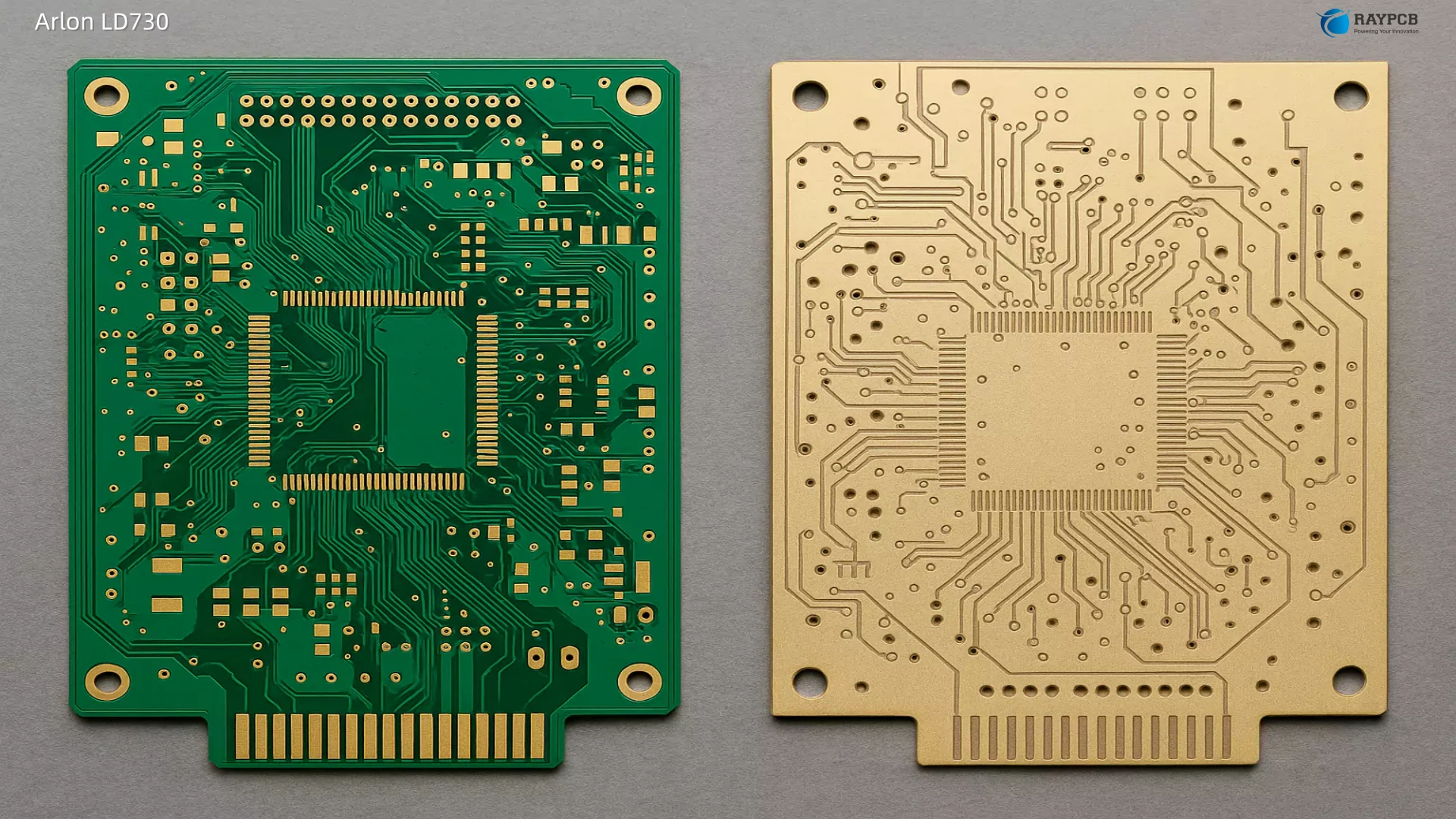

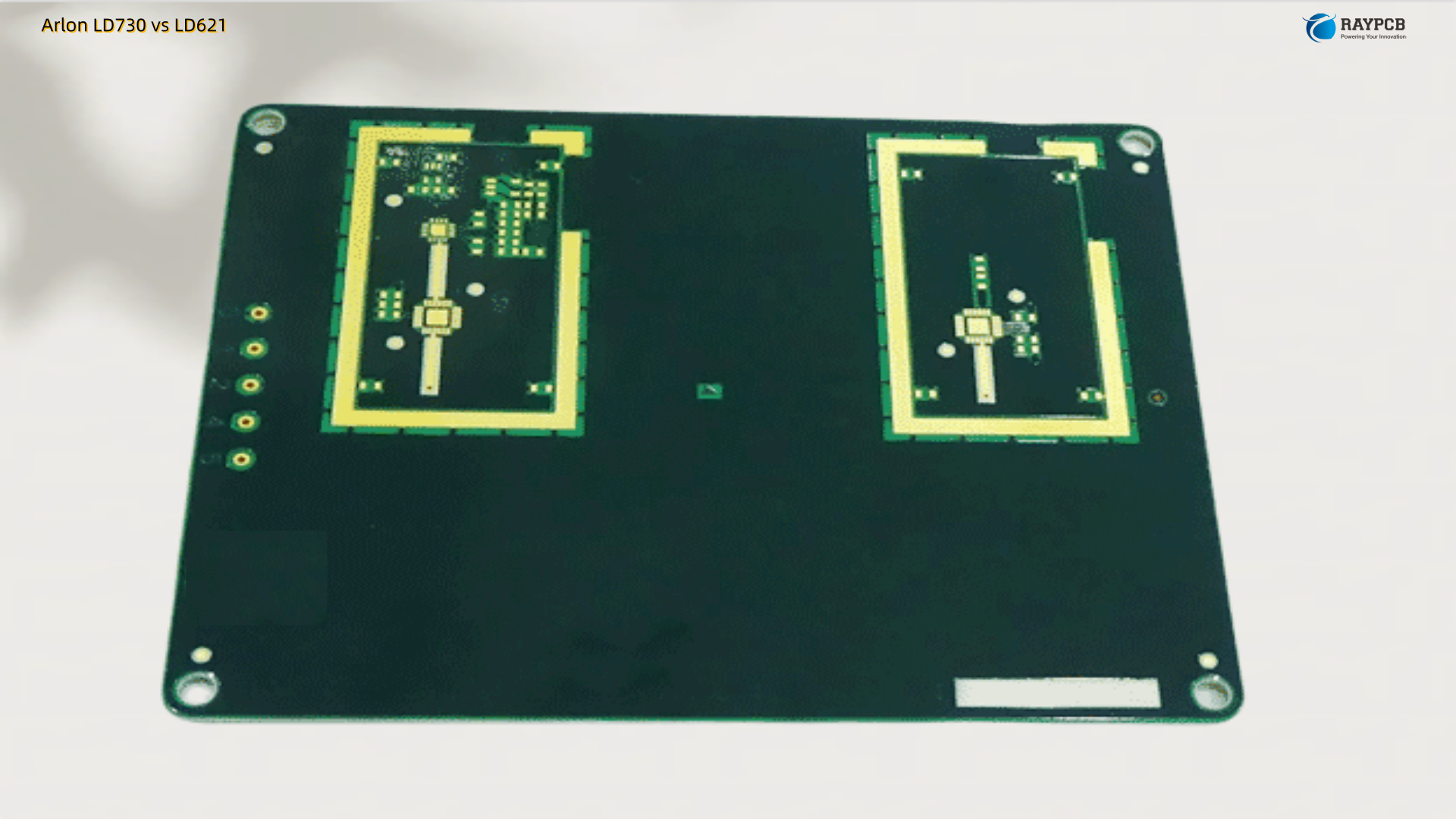

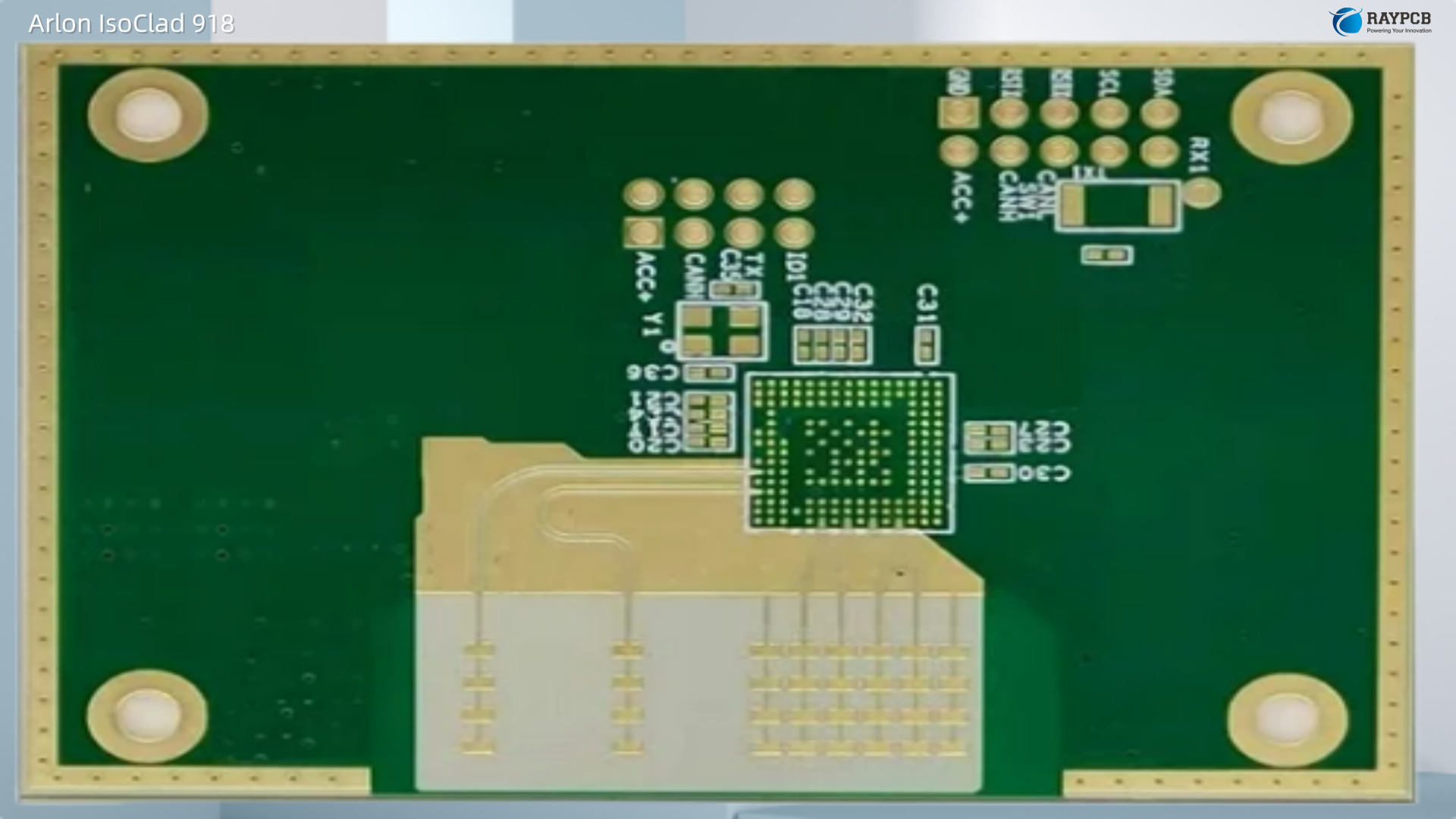

PTFE (polytetrafluoroethylene) substrates offer excellent high-frequency properties — low dielectric constant, stable Dk over temperature, and very low loss tangent. However, PTFE’s CTE behavior is more complex. While Z-axis CTE can be controlled with ceramic fillers (as in Rogers’ RO4000 series), pure PTFE tends toward higher X/Y CTE values, which complicates dimensional control during fabrication. The Rogers RO4350B specifically addresses this with a hydrocarbon-ceramic composition that delivers Z-axis CTE around 32 ppm/°C while enabling standard FR-4 compatible processing. For designs requiring both RF performance and solid CTE management, Arlon PCB materials are another well-established option in the RF laminate space.

Ceramic Substrates

Alumina (Al₂O₃) and aluminum nitride (AlN) ceramics deliver isotropic CTE values in the 4–7 ppm/°C range — genuinely matched to silicon devices. Add thermal conductivity values of 20–200 W/mK (compared to FR-4’s 0.3–0.4 W/mK) and you have materials purpose-built for power electronics, high-brightness LEDs, and automotive modules where heat dissipation and component-substrate CTE compatibility are both critical constraints. The cost and specialized processing requirements mean ceramics remain reserved for demanding applications where FR-4 simply cannot meet the reliability targets.

CTE Mismatch Failure Modes: A Diagnostic Reference

When reviewing field failures or running reliability analysis, it helps to map symptoms directly to likely CTE-related root causes.

Table 2: CTE Failure Modes and Root Causes

| Failure Symptom | Primary CTE Driver | Most Likely Root Cause |

| PTH barrel cracks | High Z-axis CTE | FR-4 with >6:1 via aspect ratio, cycling above 85°C |

| BGA corner ball open | X/Y CTE mismatch | Ceramic component on FR-4; inadequate underfill |

| Via neck fracture (HDI) | Z-axis CTE at Tg | Operating above Tg; insufficient resin content |

| Pad lifting | Z-axis CTE + moisture | Moisture-driven delamination during reflow |

| Solder joint fatigue | X/Y CTE mismatch | Repeated cycling, especially with large LCCCs |

| Delamination between layers | Z-axis CTE at Tg | High Tg exceedance + absorbed moisture |

| Trace lifting on flex | Substrate CTE vs. copper | PTFE or polyimide with poor adhesion prep |

Design Strategies to Manage CTE PCB Substrate Stress

Material selection is the primary lever, but layout and manufacturing choices also matter significantly.

Symmetrical Stack-Ups

Asymmetric layer structures create unbalanced CTE-driven stress that can warp boards during reflow or over operational temperature swings. Mirror your stack-up — match material types, copper weight, and prepreg thickness symmetrically about the board center. This is standard practice but still surprisingly often overlooked in fast-moving design cycles.

Via Design for Z-Axis CTE Management

For high-reliability designs, filled and capped vias significantly outperform unfilled barrels in thermal cycling. Copper via fill eliminates the differential between substrate expansion and hollow copper barrel expansion. For HDI designs specifically, choosing a laminate with a low-Z-axis CTE resin system is non-negotiable — any resin that manages Z-axis expansion to below 50 ppm/°C before Tg will substantially extend PTH fatigue life.

Underfill for BGA and Flip-Chip Components

Underfill epoxy — applied beneath BGAs and flip-chip components — distributes CTE-driven shear stress across the entire die footprint rather than concentrating it in corner solder balls. It’s an essential reliability tool for ceramic-packaged devices on FR-4 substrates. Select underfill materials with CTE values intermediate between the component and the substrate to avoid simply relocating the stress concentration.

Thermal Via Arrays and Copper Spreading

Strategic thermal via placement under high-power components reduces the temperature delta across the board, directly reducing the magnitude of CTE-driven dimensional changes. More uniform temperature distribution means less localized stress. Increasing copper weight in ground and power planes also improves thermal spreading, reducing hot spots that would otherwise drive elevated local CTE excursions.

Table 3: Design Mitigation Techniques vs. CTE Failure Mode

| CTE Failure Risk | Recommended Mitigation | Priority |

| PTH barrel cracking (high aspect ratio) | Copper via fill; upgrade to high-Tg material | Critical |

| BGA solder joint fatigue (CTE mismatch) | Underfill; CTE-matched substrate selection | High |

| Board warpage during reflow | Symmetrical stack-up; controlled copper balance | High |

| Delamination in harsh environments | Low Z-axis CTE resin; controlled Tg margin | High |

| HDI via neck fractures | Low Z-axis CTE prepreg; limit reflow cycles | Critical |

| Trace lifting on PTFE boards | Surface preparation (plasma or chemical treatment) | Medium |

Measuring and Characterizing CTE: Differential Thermal Analysis

For anyone doing materials qualification or investigating field failures, Differential Thermal Analysis (DTA) or Thermomechanical Analysis (TMA) are the go-to techniques for measuring CTE and identifying Tg accurately. TMA is particularly useful because it directly measures dimensional change as a function of temperature, making it the most direct way to characterize the Z-axis CTE of a laminate sample. DTA detects the thermal events (including the glass transition) by measuring heat flow differences between a test sample and an inert reference.

If you’re qualifying a new laminate for a high-reliability program, don’t rely solely on datasheet values — run TMA on your actual laminate lot. Variations in weave style, resin content, and fiber sizing between manufacturer batches can produce measurable CTE variation even within the same nominal grade.

Selecting the Right CTE PCB Substrate for Your Application

The table below maps common application categories to appropriate substrate choices, considering CTE requirements alongside other key parameters.

Table 4: Application-Driven Substrate Selection Guide

| Application | Key CTE Concern | Recommended Substrate | Notes |

| Consumer electronics | Moderate — cost-driven | Standard FR-4 | Fine for limited thermal cycling |

| Industrial control | Z-axis, high cycle life | High-Tg FR-4 (Tg 150–170°C) | Lead-free assembly compatible |

| Automotive electronics | X/Y and Z-axis, -40 to 125°C | High-Tg FR-4 or polyimide | AEC-Q standards often apply |

| Aerospace / Defense | All axes, extreme range | Polyimide | MIL-spec qualification common |

| RF / Microwave | X/Y stability, Dk stability | Rogers RO4000 series / PTFE | CTE compatible with FR-4 processing (RO4350B) |

| LED lighting (high-power) | Z-axis, heat dissipation | Metal-core (MCPCB) or ceramic | Thermal conductivity priority |

| Power electronics / EV | Component-to-substrate match | Ceramic (AlN, Al₂O₃) | Near-silicon CTE matching |

| Flexible / wearable | Dynamic flex cycling | Polyimide flex | CTE must accommodate bending radius |

Useful Resources for PCB Engineers

The following resources are worth bookmarking for substrate CTE data, design tools, and deeper technical reference:

Laminate Datasheets and Material Databases

- Rogers Corporation Material Explorer — Comprehensive datasheets for all Rogers RF laminates including CTE, Dk, Df

- Isola Group Laminates — FR-4, polyimide, and high-speed digital laminates with full thermal property data

- Panasonic Industrial Devices – MEGTRON Series — Low-loss and high-Tg material data

- IPC-4101 Standard — Industry standard specification for base materials including CTE requirements

Design and Reliability References

- IPC-2221B Generic Standard on Printed Board Design — Via design guidelines including CTE considerations

- IPC-TM-650 Test Methods Manual — Standard methods for CTE measurement and thermal characterization

- NIST Material Properties Database — Reference data for thermal expansion of metals and polymers

Learning and Technical Communities

- IPC APEX EXPO Proceedings — Annual technical papers covering laminate reliability and CTE testing

- Printed Circuit Engineering Association (PCEA) — PCB West and technical seminars on advanced laminates

Frequently Asked Questions About CTE PCB Substrate

What is a good CTE value for a PCB substrate?

For the X/Y plane, a CTE value between 11 and 18 ppm/°C is typical for FR-4 class materials and generally compatible with copper conductors (~17 ppm/°C). For the Z-axis, target below 70 ppm/°C for standard designs and below 55 ppm/°C for high-reliability or high-cycling applications. Ceramic substrates achieve 4–7 ppm/°C across all axes and offer the best match to silicon components, though at substantially higher cost.

Why does Z-axis CTE matter more than X/Y CTE?

The woven glass reinforcement in most rigid laminates constrains in-plane (X/Y) expansion significantly, keeping those values relatively close to copper. The Z-axis has no such reinforcement — only the resin system governs out-of-plane expansion. Since plated through-holes run the full board thickness in the Z-direction, they experience the full impact of the substrate-copper CTE mismatch on every thermal cycle. This is why Z-axis CTE is typically 3–5× higher than X/Y CTE in glass-weave laminates.

How does CTE relate to the glass transition temperature (Tg)?

Below Tg, a laminate’s CTE is relatively stable. As temperature rises through and above Tg, the resin softens and Z-axis CTE increases steeply — in some materials more than doubling. This is why high-Tg materials are preferred for applications with elevated operating temperatures: they maintain tighter CTE control over a wider temperature range. Always select a substrate whose Tg is comfortably above the maximum expected operating temperature, with additional margin for reflow excursions.

Can I use standard FR-4 for automotive PCBs?

It depends on the specific application and the thermal cycling profile. Automotive under-hood electronics often see temperature swings from -40°C to 125°C or higher, which represents a demanding cycling environment. Standard FR-4 (Tg ~130°C) would be borderline or insufficient for under-hood applications. High-Tg FR-4 (Tg 150–170°C) is more appropriate, and polyimide is the choice for the most demanding locations. The AEC-Q standard test protocols for automotive reliability are a useful guide for material qualification.

What is the best way to reduce CTE-related solder joint failures under BGAs?

The most effective combination is: (1) substrate selection to minimize the CTE delta between the component package and PCB — for ceramic BGAs, consider a low-CTE laminate or a CTE-matched core material; (2) underfill application to distribute shear stress across the full component footprint; and (3) thermal management to reduce the temperature excursion during operation, thereby reducing the magnitude of differential expansion on every cycle. For very large ceramic packages on FR-4, underfill is essentially mandatory if the assembly must pass automotive or MIL-spec thermal cycling.

Understanding CTE PCB substrate behavior is one of the most practical reliability skills a PCB engineer can develop. It’s not glamorous, but it’s the kind of fundamental knowledge that separates boards that survive the field from those that don’t. Spec the right laminate, account for Z-axis expansion in your via design, and use underfill where the mismatch is severe — and your products will thank you for it with fewer returns.